EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 396

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

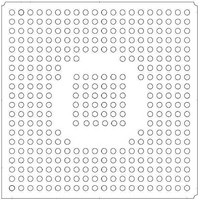

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 396 of 824

- Download datasheet (13Mb)

10

10-2

DMA Controller

EP93xx User’s Guide

10.1.2 Managing Data Transfers Using a DMA Channel

A set of control and status registers are available to the system processor for setting up DMA

operations and monitoring their status, and monitoring system interrupts generated when any

of the DMA channels wish to inform the processor to update the buffer descriptor. The DMA

controller can service 10 out of 20 possible peripherals using the 10 internal M2P/P2M DMA

channels, each with its own peripheral DMA bus capable of transferring data in both

directions simultaneously.

The UART1/2/3 and IrDA can each use two DMA channels, one for transmit and one for

receive. The AC’97 interface can use six DMA channels (three transmit and three receive) to

allow different sample frequency data queues to be handled with low software overhead. The

I

up to six channels of audio out and six channels of audio in.

To perform block moves of data from one memory address space to another with minimum of

program effort and time the DMA controller includes a memory-to-memory transfer feature.

An M2M software trigger capability is provided. It can also fill a block of memory with data

from a single location.

A hardware trigger is also provided for internal peripherals (IDE or SSP) or for external

peripherals which don’t use a handshaking protocol, to allow data streams between their

internal memory location (or the SMC) and the system memory.

For byte or word wide peripherals, the DMA can be programmed to request byte- or word-

wide AHB transfers respectively.

The transfer is completed when the Byte Count Register of the active buffer descriptor

reaches zero. Status bits will indicate if the actual byte count is equal to the programmed limit.

Completion of transfer will cause a DMA interrupt on that channel and rollover to the “other”

buffer descriptor, if configured.

2

S interface can also use up to six DMA channels (three transmit and three receive) to allow

• Five hardware requests for M2M transfers; 2 for external peripherals that follow the

• Independent source and destination address registers. Source and destination can be

• Two buffer descriptors per M2P/P2M and M2M channel to avoid potential data

• For the internal M2P/P2M channels, buffer size is independent of the peripheral’s packet

• Per channel maskable interrupt generation.

• For DMA Data transfer sizes, byte, word and quad-word data transfers are supported

• Per-channel clock gating reduces power in channels which have not been enabled by

handshake protocol, and 3 simple requests from IDE, SSPRx and SSPTx.

programmed to auto-increment or not for Memory-to-Memory channels.

underflow/overflow due to software introduced latency.

size. Transfers can automatically switch between buffers.

using a 16-byte data bay. Programmable max data transfer size per M2M channel.

software.

Copyright 2007 Cirrus Logic

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc