EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 404

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 404 of 824

- Download datasheet (13Mb)

10

10-10

10.1.10.1.1 DMA_IDLE

10.1.10.1.2 DMA_STALL

DMA Controller

EP93xx User’s Guide

10.1.10 M2M DMA Functional Description

10.1.10.1 M2M DMA Control Finite State Machine

BCR_EQ_BWC

Each DMA M2M channel is controlled by 2 finite state machines (FSM) which determine

whether the channel is transferring data to or from memory, which buffer from the double-

buffer descriptor set it is using, and whether it is currently generating an interrupt.

The DMA M2M Control FSM always resets to the DMA_IDLE state.

The DMA Control M2M FSM always enters the DMA_IDLE state when a channel is disabled

(CONTROL[3]).

The DMA Control M2M FSM exits the DMA_IDLE state and moves to the DMA_STALL state

when the ENABLE bit of the CONTROL register is set.

The DMA M2M Control FSM enters the DMA_STALL state when an M2M channel is enabled.

No STALL interrupt is generated for this condition.

The DMA M2M Control FSM enters the DMA_STALL state when a memory-to-memory

transfer has completed successfully. The DONE and STALL interrupts are generated for this

condition, if enabled.

DMA_BWC_WAIT

DMA_MEM_WR

DISABLE

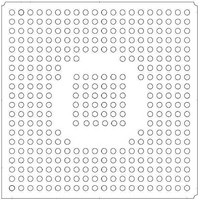

Figure 10-2. M2M DMA Control Finite State Machine

DISABLE

RX_TFR_END

Copyright 2007 Cirrus Logic

RX_TFR_END

TX_TFR_END

DMA_IDLE

DISABLE

DISABLE

DMA_MEM_RD

ENABLE

DONE/DEOT

DMA_STALL

(START, DREQ,

or TXREQ)

and BCR_VALID

IDEREQ, RXREQ,

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc