EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 210

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

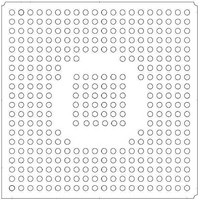

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 210 of 824

- Download datasheet (13Mb)

7

7-28

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7.4.10 Video Timing

The video timing circuitry consists of a horizontal down counter and a vertical down counter.

Signal timing for a specific video format is generated by programmable values that are

compared to the count values.

An AC signal is generated to support either bias voltage switching for LCDs or a field

indicator for interlaced video. The An AC signal, if ACEN = ‘1’ in the

output on the P[17] pin. The toggle rate of the AC signal is selected by writing to the

register.

LCD shifting signals, XECL and YSCL, are generated to support simple LCDs. These signals,

if LCDEN = ‘1’ in the

respectively. XECL is generated every 64 pixel clocks. YSCL is the inversion of HSYNCn.

The Raster Engine provides an end of frame interrupt, when enabled, to the interrupt

controller. This interrupt defines when the last information has been sent to the display for the

current frame. It indicates the start of an interval when changes can be made to the LUT or

source for the displayed image without affecting the display. It must be configured as an edge

triggered interrupt. Changes such as a new cursor location or a new screen image location

automatically change at this time, under hardware control. The interval for making LUT

changes, etc. without affecting the displayed image depends on the display’s technology. The

time duration is equal to the vertical blanking interval (VLinesTotal duration - VACTIVE

duration).

In addition, the programmable VCLR and HCLR fields in the

a secondary interrupt during normal operation, where the interrupt can be programmed to

trigger at any vertical and horizontal counter combination.

The frequency of the clock used for video timing and the entire video pipeline must meet the

requirements of the display type. The video clock frequency is selected by writing to the

VidClkDiv

corresponds to a 1280 pixels by 1024 pixels display size, and non-interlaced video at a 80Hz

frame refresh.

The programmed values for the video timing section of the raster engine are shown in

Figure 7-9, "Progressive/Dual Scan Video Signals"

Signals". Independent horizontal and vertical down counters are used as a reference for all

other signals. The synchronization, blanking, and active video control signalling is generated

by comparing programmed values to the counters.

Note: Total Bus/SDRAM bandwidth is shared between the Raster Engine and other device

controllers. The pixel depth, display size, and display refresh rate can be limited by the

Bus/SDRAM bandwidth that is available to the Raster Engine.

register (see

“VideoAttribs”

Chapter

Copyright 2007 Cirrus Logic

5). The video circuitry is targeted to run up to 132MHz. This

register, are output on pixel data pins P[16] and P[15],

and

Figure 7-10, "Interlaced Video

“SigClrStr”

“VideoAttribs”

register are used as

register, is

“ACRate”

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc