EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 324

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

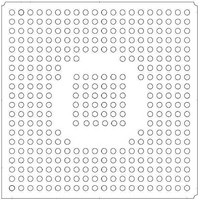

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 324 of 824

- Download datasheet (13Mb)

9

9-22

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9.2.3.3 Receive Errors

Refer to the circled numbers in

Receive error conditions are broken into two categories: hard errors and soft errors. A hard

error is generally considered a reliability problem. This includes AHB bus access problems. A

soft error indicates that the frame was not successfully received. The error may be expected

or rare. A soft error needs a graceful recovery by the host driver. Soft errors include: CRC

errors, receiver over-run, frames too long, or frames too short. Hard errors are parity errors

(when enabled), system errors, and master or target aborts, these errors will stop receive

DMA activity, and require host intervention for recovery. Recovery may be achieved by

performing a RxChRes (Bus Master Control) and reinitializing.

Note:

Note: Steps 1, 11, and 13 are transparent to the MAC. Steps 2 through 10 and 12 directly involve

1. Driver initializes some number of receive descriptors.

2. Driver writes RXDEnq register with the additional number of receive descriptors.

3. On-chip Descriptor Processor fetches descriptors into internal FIFO decrements

4. The address of the next receive data buffer is loaded into the Receive Buffer Current

5. A frame is received from the LAN medium.

6. The MAC Engine passes the frame data to the Receive Data FIFO.

7. The Receive Descriptor Processor stores the frame data into system memory.

8. End of frame status is written to the Receive Status Queue the RXStsEnq value reduced

9. Driver interrupted if interrupt conditions met.

10.Received frame passed to the protocol stack.

11.Driver clears the Receive Frame Processed bit in Status Queue.

12.Driver writes number of entries processed in the status queue, freeing them for future

13.After the driver gets the used receive buffers back from the stack, the driver may repeat

RXDEnq appropriately.

Address.

by one.

use by the MAC.

step 2.

the MAC.

Steps 5, 6, and 7 can overlap.

Copyright 2007 Cirrus Logic

Figure

9-9. The detailed receive flow is:

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc