DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 37

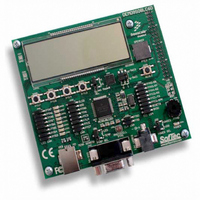

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 37 of 360

- Download datasheet (4Mb)

before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to

PPDACK, then the pins will switch to their reset states when PPDACK is written.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that

interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before

writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O

latches are opened.

3.6.3

Stop1 mode is entered by executing a STOP instruction under the conditions as shown in

of the internal circuitry of the MCU is powered off in stop1, providing the lowest possible standby current.

Upon entering stop1, all I/O pins automatically transition to their default reset states.

Exit from stop1 is performed by asserting the wake-up pins or RESET or IRQ.

In addition, the real-time interrupt (RTI) can wake the MCU from stop1 if enabled.

Upon wake-up from stop1 mode, the MCU starts up as from a power-on reset (POR):

In addition to the above, upon waking up from stop1, the PDF bit in SPMSC2 is set. This flag is used to

direct user code to go to a stop1 recovery routine. PDF remains set until a 1 is written to PPDACK in

SPMSC2.

3.6.4

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even

in the exception case (ENBDM = 1), where clocks to the background debug logic continue to operate,

clocks to the peripheral systems are halted to reduce power consumption. Refer to

Mode,”

behavior in stop modes.

Freescale Semiconductor

•

•

•

All module control and status registers are reset

The LVD reset function is enabled and the MCU remains in the reset state if V

trip point (low trip point selected due to POR)

The CPU takes the reset vector

Section 3.6.2, “Stop2

Stop1 Mode

On-Chip Peripheral Modules in Stop Modes

IRQ always functions as an active-low wakeup input when the MCU is in

stop1, regardless of how the pin is configured before entering stop1.

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Mode,” and

Section 3.6.1, “Stop3

NOTE

Mode,” for specific information on system

Chapter 3 Modes of Operation

Section 3.6.3, “Stop1

DD

is below the LVD

Table

3-1. Most

37

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: