DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 284

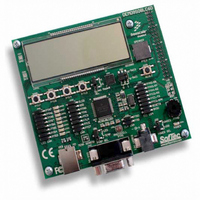

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 284 of 360

- Download datasheet (4Mb)

Chapter 15 Analog-to-Digital Converter (S08ADC12V1)

digital value of the analog signal. The result of the conversion is transferred to ADCRH and ADCRL upon

completion of the conversion algorithm.

If the bus frequency is less than the f

cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th

of the f

sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in

The maximum total conversion time is determined by the clock source chosen and the divide ratio selected.

The clock source is selectable by the ADICLK bits, and the divide ratio is specified by the ADIV bits. For

example, in 10-bit mode, with the bus clock selected as the input clock source, the input clock divide-by-1

ratio selected, and a bus frequency of 8 MHz, then the conversion time for a single conversion is:

284

Single or first continuous 10-bit or 12-bit

Single or first continuous 10-bit or 12-bit

Single or first continuous 10-bit or 12-bit

Single or first continuous 10-bit or 12-bit

Subsequent continuous 10-bit or 12-bit;

Subsequent continuous 10-bit or 12-bit;

ADCK

Single or first continuous 8-bit

Single or first continuous 8-bit

Single or first continuous 8-bit

Single or first continuous 8-bit

Subsequent continuous 8-bit;

Subsequent continuous 8-bit;

frequency, precise sample time for continuous conversions cannot be guaranteed when long

Conversion Type

Conversion time =

f

f

BUS

BUS

The ADCK frequency must be between f

maximum to meet ADC specifications.

f

f

BUS

BUS

> f

> f

> f

> f

ADCK

ADCK

ADCK

ADCK

Number of bus cycles = 3.5 μs x 8 MHz = 28 cycles

Table 15-12. Total Conversion Time vs. Control Conditions

/11

/11

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

ADCK

23 ADCK cyc

8 MHz/1

frequency, precise sample time for continuous conversions

ADICLK

0x, 10

0x, 10

0x, 10

0x, 10

11

11

11

11

xx

xx

xx

xx

NOTE

ADLSMP

+

ADCK

0

0

1

1

0

0

1

1

0

0

1

1

5 bus cyc

minimum and f

8 MHz

20 ADCK cycles + 5 bus clock cycles

23 ADCK cycles + 5 bus clock cycles

40 ADCK cycles + 5 bus clock cycles

43 ADCK cycles + 5 bus clock cycles

5 μs + 20 ADCK + 5 bus clock cycles

5 μs + 23 ADCK + 5 bus clock cycles

5 μs + 40 ADCK + 5 bus clock cycles

5 μs + 43 ADCK + 5 bus clock cycles

Max Total Conversion Time

= 3.5 μs

ADCK

17 ADCK cycles

20 ADCK cycles

37 ADCK cycles

40 ADCK cycles

Table

Freescale Semiconductor

15-12.

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: