DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 225

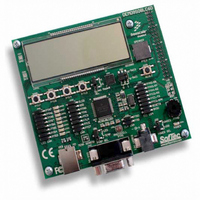

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 225 of 360

- Download datasheet (4Mb)

1

12.2.7

This register is actually two separate registers. Reads return the contents of the read-only receive data

buffer and writes go to the write-only transmit data buffer. Reads and writes of this register are also

involved in the automatic flag clearing mechanisms for the SCI status flags.

Freescale Semiconductor

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

Reset

TXINV

TXDIR

Field

ORIE

NEIE

FEIE

PEIE

5

4

3

2

1

0

W

R

1

SCI Data Register (SCID)

TxD Pin Direction in Single-Wire Mode — When the SCI is configured for single-wire half-duplex operation

(LOOPS = RSRC = 1), this bit determines the direction of data at the TxD pin.

0 TxD pin is an input in single-wire mode.

1 TxD pin is an output in single-wire mode.

Transmit Data Inversion — Setting this bit reverses the polarity of the transmitted data output.

0 Transmit data not inverted

1 Transmit data inverted

Overrun Interrupt Enable — This bit enables the overrun flag (OR) to generate hardware interrupt requests.

0 OR interrupts disabled (use polling).

1 Hardware interrupt requested when OR = 1.

Noise Error Interrupt Enable — This bit enables the noise flag (NF) to generate hardware interrupt requests.

0 NF interrupts disabled (use polling).

1 Hardware interrupt requested when NF = 1.

Framing Error Interrupt Enable — This bit enables the framing error flag (FE) to generate hardware interrupt

requests.

0 FE interrupts disabled (use polling).

1 Hardware interrupt requested when FE = 1.

Parity Error Interrupt Enable — This bit enables the parity error flag (PF) to generate hardware interrupt

requests.

0 PF interrupts disabled (use polling).

1 Hardware interrupt requested when PF = 1.

R7

T7

0

7

Table 12-7. SCIC3 Register Field Descriptions (continued)

R6

T6

0

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Figure 12-12. SCI Data Register (SCID)

R5

T5

0

5

R4

T4

0

4

Description

Chapter 12 Serial Communications Interface (S08SCIV3)

R3

T3

3

0

R2

T2

0

2

R1

T1

0

1

R0

T0

0

0

225

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: