DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 172

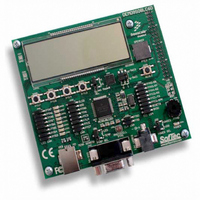

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 172 of 360

- Download datasheet (4Mb)

Chapter 10 Internal Clock Generator (S08ICGV4)

10.2.2

This is a high-level description only. Detailed descriptions of operating modes are contained in

Section 10.5, “Functional

172

•

•

•

•

•

•

•

•

•

•

•

•

Digitally-controlled oscillator (DCO) preserves previous frequency settings, allowing fast

frequency lock when recovering from stop3 mode

DCO will maintain operating frequency during a loss or removal of reference clock

Post-FLL divider selects 1 of 8 bus rate divisors (/1 through /128)

Separate self-clocked source for real-time interrupt

Trimmable internal clock source supports SCI communications without additional external

components

Automatic FLL engagement after lock is acquired

External oscillator selectable for low power or high gain

Mode 1 — Off

The output clock, ICGOUT, is static. This mode may be entered when the STOP instruction is

executed.

Mode 2 — Self-clocked (SCM)

Default mode of operation that is entered immediately after reset. The ICG’s FLL is open loop and

the digitally controlled oscillator (DCO) is free running at a frequency set by the filter bits.

In this mode, the ICG’s FLL is used to create frequencies that are programmable multiples of the

internal reference clock.

— FLL engaged internal unlocked is a transition state that occurs while the FLL is attempting to

— FLL engaged internal locked is a state that occurs when the FLL detects that the DCO is locked

Mode 4 — FLL bypassed external (FBE)

In this mode, the ICG is configured to bypass the FLL and use an external clock as the clock source.

Mode 5 — FLL engaged external (FEE)

The ICG’s FLL is used to generate frequencies that are programmable multiples of the external

clock reference.

— FLL engaged external unlocked is a transition state that occurs while the FLL is attempting to

— FLL engaged external locked is a state which occurs when the FLL detects that the DCO is

Mode 3 — FLL engaged internal (FEI)

Modes of Operation

lock. The FLL DCO frequency is off target and the FLL is adjusting the DCO to match the

target frequency.

to a multiple of the internal reference.

lock. The FLL DCO frequency is off target and the FLL is adjusting the DCO to match the

target frequency.

locked to a multiple of the internal reference.

Description.”

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: