D12363VF33V Renesas Electronics America, D12363VF33V Datasheet - Page 638

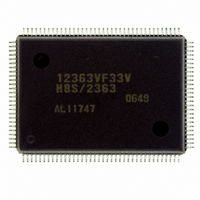

D12363VF33V

Manufacturer Part Number

D12363VF33V

Description

IC H8S/2363 MCU ROMLESS 128QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2300r

Specifications of D12363VF33V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

33MHz

Connectivity

I²C, IrDA, SCI, SmartCard

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

84

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 10x10b, D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

128-QFP

For Use With

YR0K42378FC000BA - KIT EVAL FOR H8S/2378

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D12363VF33V

Manufacturer:

ST

Quantity:

67 000

Company:

Part Number:

D12363VF33V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

D12363VF33V

Manufacturer:

RENSAS

Quantity:

20 000

- Current page: 638 of 1044

- Download datasheet (6Mb)

Section 14 Serial Communication Interface (SCI, IrDA)

14.4.2

In asynchronous mode, the SCI operates on a basic clock with a frequency of 16 times the bit rate.

In reception, the SCI samples the falling edge of the start bit using the basic clock, and performs

internal synchronization. Receive data is latched at the middle of each bit by sampling the data at

the rising edge of the 8th pulse of the basic clock as shown in figure 14.3. Thus the reception

margin in asynchronous mode is given by formula (1) below.

Where M: Reception Margin

Assuming values of F = 0 and D = 0.5 in formula (1), a reception margin is given by formula

below.

M = {0.5 – 1/(2 × 16)} × 100 [%] = 46.875%

However, this is only the computed value, and a margin of 20% to 30% should be allowed in

system design.

Rev.6.00 Mar. 18, 2009 Page 578 of 980

REJ09B0050-0600

M = { (0.5 –

Internal base

clock

Receive data

(RxD)

Synchronization

sampling timing

Data sampling

timing

N: Ratio of bit rate to clock (N = 16)

D: Clock duty (D = 0.5 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute value of clock rate deviation

Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

Figure 14.3 Receive Data Sampling Timing in Asynchronous Mode

2N

1

) – (L – 0.5) F –

0

8 clocks

Start bit

16 clocks

7

D – 0.5

N

(1 + F) }

15 0

100 [%]

D0

7

... Formula (1)

15 0

D1

Related parts for D12363VF33V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: