D12363VF33V Renesas Electronics America, D12363VF33V Datasheet - Page 44

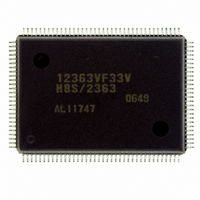

D12363VF33V

Manufacturer Part Number

D12363VF33V

Description

IC H8S/2363 MCU ROMLESS 128QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2300r

Specifications of D12363VF33V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

33MHz

Connectivity

I²C, IrDA, SCI, SmartCard

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

84

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 10x10b, D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

128-QFP

For Use With

YR0K42378FC000BA - KIT EVAL FOR H8S/2378

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

D12363VF33V

Manufacturer:

ST

Quantity:

67 000

Company:

Part Number:

D12363VF33V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

D12363VF33V

Manufacturer:

RENSAS

Quantity:

20 000

- Current page: 44 of 1044

- Download datasheet (6Mb)

Figure 6.52 Example of Idle Cycle Operation after DRAM Access (Write after Read)

Figure 6.53 Example of Idle Cycle Operation after DRAM Write Access

Figure 6.54 Example of Timing for Idle Cycle Insertion in Case of Consecutive Read

Figure 6.55 Example of Timing when Write Data Buffer Function is Used ............................. 205

Figure 6.56 Bus Released State Transition Timing ................................................................... 208

Section 7 DMA Controller (DMAC)

Figure 7.1

Figure 7.2

Figure 7.3

Figure 7.4

Figure 7.5

Figure 7.6

Figure 7.7

Figure 7.8

Figure 7.9

Figure 7.10 Example of Single Address Mode Setting Procedure

Figure 7.11 Operation in Normal Mode .................................................................................... 260

Figure 7.12 Example of Normal Mode Setting Procedure......................................................... 261

Figure 7.13 Operation in Block Transfer Mode (BLKDIR = 0)................................................ 263

Figure 7.14 Operation in Block Transfer Mode (BLKDIR = 1)................................................ 264

Figure 7.15 Operation Flow in Block Transfer Mode ............................................................... 265

Figure 7.16 Example of Block Transfer Mode Setting Procedure............................................. 266

Figure 7.17 Example of DMA Transfer Bus Timing................................................................. 267

Figure 7.18 Example of Short Address Mode Transfer............................................................. 268

Figure 7.19 Example of Full Address Mode Transfer (Cycle Steal) ......................................... 269

Figure 7.20 Example of Full Address Mode Transfer (Burst Mode)......................................... 270

Figure 7.21 Example of Full Address Mode Transfer (Block Transfer Mode) ......................... 271

Figure 7.22 Example of DREQ Pin Falling Edge Activated Normal Mode Transfer................ 272

Figure 7.23 Example of DREQ Pin Falling Edge Activated Block Transfer Mode Transfer.... 273

Figure 7.24 Example of DREQ Pin Low Level Activated Normal Mode Transfer................... 274

Figure 7.25 Example of DREQ Pin Low Level Activated Block Transfer Mode Transfer....... 275

Figure 7.26 Example of Single Address Mode Transfer (Byte Read) ....................................... 276

Figure 7.27 Example of Single Address Mode (Word Read) Transfer...................................... 276

Figure 7.28 Example of Single Address Mode Transfer (Byte Write) ...................................... 277

Figure 7.29 Example of Single Address Mode Transfer (Word Write)..................................... 278

Rev.6.00 Mar. 18, 2009 Page xlii of lviii

REJ09B0050-0600

(IDLC = 0, RAST = 0, CAST = 0)......................................................................... 199

(IDLC = 0, ICIS1 = 0, RAST = 0, CAST = 0) ....................................................... 200

and Write Accesses to DRAM Space in RAS Down Mode ................................... 203

Block Diagram of DMAC ...................................................................................... 214

Areas for Register Re-Setting by DTC (Channel 0A) ............................................ 239

Operation in Sequential Mode................................................................................ 247

Example of Sequential Mode Setting Procedure.................................................... 248

Operation in Idle Mode .......................................................................................... 249

Example of Idle Mode Setting Procedure .............................................................. 251

Operation in Repeat mode...................................................................................... 254

Example of Repeat Mode Setting Procedure.......................................................... 255

Operation in Single Address Mode (When Sequential Mode is Specified)............ 257

(When Sequential Mode is Specified).................................................................... 258

Related parts for D12363VF33V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: