CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 9

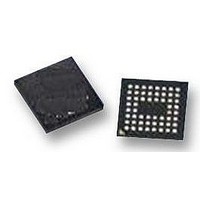

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

3.11

3.12

3.12.1

3.12.2

• 3× 64 bytes

• 8 × 512 bytes (Endpoints 2, 4, 6, 8)

• EP0

• Bidirectional endpoint zero, 64-byte buffer

• EP1IN, EP1OUT

• 64-byte buffers, bulk or interrupt

• EP2,4,6,8

• Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4

and EP8 can be double buffered, while EP2 and 6 can be

either double, triple, or quad buffered. For high-speed end-

point configuration options, see Figure 3-5.

Register Addresses

Endpoint RAM

Size

Organization

(Endpoints 0 and 1)

F000

EFFF

FFFF

E800

E7FF

E7C0

E780

E740

E700

E6FF

E500

E4FF

E47F

E400

E3FF

E1FF

E000

E7BF

E77F

E73F

E480

E200

128 bytes GPIF Waveforms

8051 Addressable Registers

64 Bytes EP0 IN/OUT

2 KBytes RESERVED

64 Bytes RESERVED

Reserved (512)

4 KBytes EP2-EP8

64 Bytes EP1OUT

64 Bytes EP1IN

Reserved (128)

8051 xdata RAM

512 bytes

(8 x 512)

buffers

3.12.3

A separate 8-byte buffer at 0xE6B8-0xE6BF holds the Set-up

data from a CONTROL transfer.

3.12.4

Endpoints 0 and 1 are the same for every configuration.

Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can

be either BULK or INTERRUPT. The endpoint buffers can be

configured in any 1 of the 12 configurations shown in the

vertical columns. When operating in full-speed BULK mode

only the first 64 bytes of each buffer are used. For example in

high-speed, the max packet size is 512 bytes but in full-speed

it is 64 bytes. Even though a buffer is configured to be a 512

byte buffer, in full-speed only the first 64 bytes are used. The

unused endpoint buffer space is not available for other opera-

tions. An example endpoint configuration would be:

(512)

Set-up Data Buffer

Endpoint Configurations (High-speed Mode)

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Page 9 of 60