CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 22

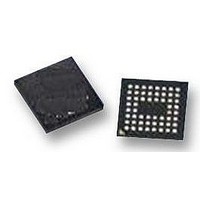

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

Table 4-1. FX2LP Pin Descriptions (continued)

TQFP

Port A

128

34

99

35

12

82

83

11

1

TQFP

100

100

28

77

10

67

68

11

SSOP

56

49

12

11

40

41

5

QFN

56

42

54

33

34

5

4

VFBGA

8G

6G

8B

1C

2C

2B

56

BKPT

RESET#

EA

XTALIN

XTALOUT

CLKOUT on

CY7C68013A

------------------

PE1 or

T1OUT on

CY7C68015A

PA0 or

INT0#

PA1 or

INT1#

Name

[10]

-----------

Output

Output

Type

Input

Input

Input

I/O/Z

I/O/Z

I/O/Z

O/Z

Default

12 MHz

----------

(PE1)

(PA0)

(PA1)

N/A

N/A

N/A

N/A

L

I

I

I

Breakpoint. This pin goes active (HIGH) when the 8051

address bus matches the BPADDRH/L registers and

breakpoints are enabled in the BREAKPT register

(BPEN = 1). If the BPPULSE bit in the BREAKPT

register is HIGH, this signal pulses HIGH for eight

12-/24-/48-MHz clocks. If the BPPULSE bit is LOW, the

signal remains HIGH until the 8051 clears the BREAK

bit (by writing 1 to it) in the BREAKPT register.

Active LOW Reset. Resets the entire chip. See section

3.9 ”Reset and Wakeup” on page 6 for more details.

External Access. This pin determines where the 8051

fetches code between addresses 0x0000 and 0x3FFF.

If EA = 0 the 8051 fetches this code from its internal

RAM. IF EA = 1 the 8051 fetches this code from external

memory.

Crystal Input. Connect this signal to a 24-MHz

parallel-resonant, fundamental mode crystal and load

capacitor to GND.

It is also correct to drive XTALIN with an external

24-MHz square wave derived from another clock

source. When driving from an external source, the

driving signal should be a 3.3V square wave.

Crystal Output. Connect this signal to a 24-MHz

parallel-resonant, fundamental mode crystal and load

capacitor to GND.

If an external clock is used to drive XTALIN, leave this

pin open.

CLKOUT: 12-, 24- or 48-MHz clock, phase locked to the

24-MHz input clock. The 8051 defaults to 12-MHz

operation. The 8051 may three-state this output by

setting CPUCS.1 = 1.

------------------------------------------------------------------------

Multiplexed pin whose function is selected by the

PORTECFG.0 bit.

PE1 is a bidirectional I/O port pin.

T1OUT is an active-HIGH signal from 8051

Timer-counter1. T1OUT outputs a high level for one

CLKOUT clock cycle when Timer1 overflows. If Timer1

is operated in Mode 3 (two separate timer/counters),

T1OUT is active when the low byte timer/counter

overflows.

Multiplexed pin whose function is selected by

PORTACFG.0

PA0 is a bidirectional IO port pin.

INT0# is the active-LOW 8051 INT0 interrupt input

signal, which is either edge triggered (IT0 = 1) or level

triggered (IT0 = 0).

Multiplexed pin whose function is selected by:

PORTACFG.1

PA1 is a bidirectional IO port pin.

INT1# is the active-LOW 8051 INT1 interrupt input

signal, which is either edge triggered (IT1 = 1) or level

triggered (IT1 = 0).

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Description

Page 22 of 60