CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 3

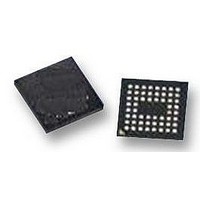

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

3.0

3.1

FX2LP operates at two of the three rates defined in the USB

Specification Revision 2.0, dated April 27, 2000:

FX2LP does not support the low-speed signaling mode of

1.5 Mbps.

3.2

The 8051 microprocessor embedded in the FX2LP family has

256 bytes of register RAM, an expanded interrupt system,

three timer/counters, and two USARTs.

3.2.1

FX2LP has an on-chip oscillator circuit that uses an external

24-MHz (±100-ppm) crystal with the following characteristics:

An on-chip PLL multiplies the 24-MHz oscillator up to

480 MHz, as required by the transceiver/PHY, and internal

counters divide it down for use as the 8051 clock. The default

8051 clock frequency is 12 MHz. The clock frequency of the

8051 can be changed by the 8051 through the CPUCS

register, dynamically.

Note:

• Full speed, with a signaling bit rate of 12 Mbps

• High speed, with a signaling bit rate of 480 Mbps.

• Parallel resonant

• Fundamental mode

• 500-∝W drive level

• 12-pF (5% tolerance) load capacitors.

1.

115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a “1” for UART0 and/or UART1, respectively.

12-pF capacitor values assumes a trace capacitance

USB Signaling Speed

8051 Microprocessor

8051 Clock Frequency

Functional Overview

of 3 pF per side on a four-layer FR4 PCA

Figure 3-1. Crystal Configuration

12 pf

C1

20 × PLL

24 MHz

12 pf

C2

The CLKOUT pin, which can be three-stated and inverted

using internal control bits, outputs the 50% duty cycle 8051

clock, at the selected 8051 clock frequency—48, 24, or 12

MHz.

3.2.2

FX2LP contains two standard 8051 USARTs, addressed via

Special Function Register (SFR) bits. The USART interface

pins are available on separate I/O pins, and are not multi-

plexed with port pins.

UART0 and UART1 can operate using an internal clock at

230 KBaud with no more than 1% baud rate error. 230-KBaud

operation is achieved by an internally derived clock source that

generates overflow pulses at the appropriate time. The

internal clock adjusts for the 8051 clock rate (48, 24, 12 MHz)

such that it always presents the correct frequency for

230-KBaud operation.

3.2.3

Certain 8051 SFR addresses are populated to provide fast

access to critical FX2LP functions. These SFR additions are

shown in Table 3-1. Bold type indicates non-standard,

enhanced 8051 registers. The two SFR rows that end with “0”

and “8” contain bit-addressable registers. The four I/O ports

A–D use the SFR addresses used in the standard 8051 for

ports 0–3, which are not implemented in FX2LP. Because of

the faster and more efficient SFR addressing, the FX2LP I/O

ports are not addressable in external RAM space (using the

MOVX instruction).

3.3

FX2LP supports the I

SCL and SDA pins have open-drain outputs and hysteresis

inputs. These signals must be pulled up to 3.3V, even if no I

device is connected.

3.4

All packages: 8- or 16-bit “FIFO” bidirectional data bus, multi-

plexed on I/O ports B and D. 128-pin package: adds 16-bit

output-only 8051 address bus, 8-bit bidirectional data bus.

USARTS

Special Function Registers

I

Buses

2

C Bus

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

2

C bus as a master only at 100-/400-KHz.

[1]

Page 3 of 60

2

C