CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 50

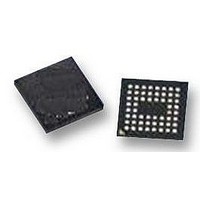

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

10.17

10.17.1 Single and Burst Synchronous Read Example

Figure 10-18 shows the timing relationship of the SLAVE FIFO

signals during a synchronous FIFO read using IFCLK as the

synchronizing clock. The diagram illustrates a single read

followed by a burst read.

FLAGS

FIFOADR

FIFO POINTER

IFCLK

SLRD

SLCS

DATA

FIFO DATA BUS

• At t = 0 the FIFO address is stable and the signal SLCS is

• At t = 1, SLOE is asserted. SLOE is an output enable only,

• At t = 2, SLRD is asserted. SLRD must meet the set-up time

SLOE

asserted (SLCS may be tied low in some applications).

Note: t

is running at 48 MHz, the FIFO address set-up time is more

than one IFCLK cycle.

whose sole function is to drive the data bus. The data that

is driven on the bus is the data that the internal FIFO pointer

is currently pointing to. In this example it is the first data

value in the FIFO. Note: the data is pre-fetched and is driven

on the bus when SLOE is asserted.

of t

edge of the IFCLK) and maintain a minimum hold time of

t

SLRD signal). If the SLCS signal is used, it must be asserted

RDH

SRD

(time from the IFCLK edge to the deassertion of the

Sequence Diagram

SFA

(time from asserting the SLRD signal to the rising

has a minimum of 25 ns. This means when IFCLK

Not Driven

t=0

IFCLK

N

t=1

Figure 10-18. Slave FIFO Synchronous Read Sequence and Timing Diagram

SLOE

t

SFA

Figure 10-19. Slave FIFO Synchronous Sequence of Events Diagram

t

OEon

Data Driven: N

t=2

Driven: N

t

SRD

IFCLK

N

t

IFCLK

t

XFD

t=3

t

RDH

SLRD

t

XFLG

t

OEoff

N+1

t=4

t

IFCLK

N+1

FAH

N+1

SLOE

SLRD

Not Driven

IFCLK

t

T=0

N+1

SFA

t

The same sequence of events are shown for a burst read and

are marked with the time indicators of T = 0 through 5. Note:

For the burst mode, the SLRD and SLOE are left asserted

during the entire duration of the read. In the burst read mode,

when SLOE is asserted, data indexed by the FIFO pointer is

on the data bus. During the first read cycle, on the rising edge

of the clock the FIFO pointer is updated and increments to

point to address N+1. For each subsequent rising edge of

IFCLK, while the SLRD is asserted, the FIFO pointer is incre-

mented and the next data value is placed on the data bus.

OEon

SLOE

• The FIFO pointer is updated on the rising edge of the IFCLK,

before SLRD is asserted (i.e., the SLCS and SLRD signals

must both be asserted to start a valid read condition).

while SLRD is asserted. This starts the propagation of data

from the newly addressed location to the data bus. After a

propagation delay of t

of IFCLK) the new data value is present. N is the first data

value read from the FIFO. In order to have data on the FIFO

data bus, SLOE MUST also be asserted.

T=2

>= t

T=1

N+1

IFCLK

N+1

SRD

N+1

SLRD

t

XFD

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

N+2

N+2

IFCLK

N+2

N+3

N+3

IFCLK

t

XFD

XFD

(measured from the rising edge

N+4

N+4

IFCLK

N+3

SLRD

t

>= t

XFD

[20]

RDH

N+4

N+4

IFCLK

t

N+4

OEoff

SLOE

T=3

T=4

t

Page 50 of 60

FAH

Not Driven

IFCLK

N+4