CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 11

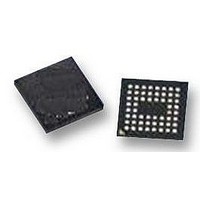

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

3.13

3.13.1

The FX2LP slave FIFO architecture has eight 512-byte blocks

in the endpoint RAM that directly serve as FIFO memories,

and are controlled by FIFO control signals (such as IFCLK,

SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).

In operation, some of the eight RAM blocks fill or empty from

the SIE, while the others are connected to the I/O transfer

logic. The transfer logic takes two forms, the GPIF for internally

generated control signals, or the slave FIFO interface for

externally controlled transfers.

3.13.2

The FX2LP endpoint FIFOS are implemented as eight physi-

cally distinct 256x16 RAM blocks. The 8051/SIE can switch

any of the RAM blocks between two domains, the USB (SIE)

domain and the 8051-I/O Unit domain. This switching is done

virtually instantaneously, giving essentially zero transfer time

between “USB FIFOS” and “Slave FIFOS.” Since they are

physically the same memory, no bytes are actually transferred

between buffers.

At any given time, some RAM blocks are filling/emptying with

USB data under SIE control, while other RAM blocks are

available to the 8051 and/or the I/O control unit. The RAM

blocks operate as single-port in the USB domain, and

dual-port in the 8051-I/O domain. The blocks can be

configured as single, double, triple, or quad buffered as previ-

ously shown.

The I/O control unit implements either an internal-master (M

for master) or external-master (S for Slave) interface.

In

FIFOADR[1..0] to select a FIFO. The RDY pins (two in the

56-pin package, six in the 100-pin and 128-pin packages) can

be used as flag inputs from an external FIFO or other logic if

desired. The GPIF can be run from either an internally derived

clock or externally supplied clock (IFCLK), at a rate that

transfers data up to 96 Megabytes/s (48-MHz IFCLK with

16-bit interface).

In Slave (S) mode, the FX2LP accepts either an internally

derived clock or externally supplied clock (IFCLK, max.

frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE,

PKTEND signals from external logic. When using an external

IFCLK, the external clock must be present before switching to

the external clock with the IFCLKSRC bit. Each endpoint can

individually be selected for byte or word operation by an

internal configuration bit, and a Slave FIFO Output Enable

signal SLOE enables data of the selected width. External logic

must insure that the output enable signal is inactive when

writing data to a slave FIFO. The slave interface can also

operate asynchronously, where the SLRD and SLWR signals

act directly as strobes, rather than a clock qualifier as in

synchronous mode. The signals SLRD, SLWR, SLOE and

PKTEND are gated by the signal SLCS#.

Master

Master/Slave Control Signals

External FIFO Interface

Architecture

(M)

mode,

the

GPIF

internally

controls

3.13.3

An 8051 register bit selects one of two frequencies for the

internally supplied interface clock: 30 MHz and 48 MHz. Alter-

natively, an externally supplied clock of 5 MHz–48 MHz

feeding the IFCLK pin can be used as the interface clock.

IFCLK can be configured to function as an output clock when

the GPIF and FIFOs are internally clocked. An output enable

bit in the IFCONFIG register turns this clock output off, if

desired. Another bit within the IFCONFIG register will invert

the IFCLK signal whether internally or externally sourced.

3.14

The GPIF is a flexible 8- or 16-bit parallel interface driven by a

user-programmable finite state machine. It allows the

CY7C68013A/15A to perform local bus mastering, and can

implement a wide variety of protocols such as ATA interface,

printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine

address outputs (GPIFADRx), and six general-purpose ready

inputs (RDY). The data bus width can be 8 or 16 bits. Each

GPIF vector defines the state of the control outputs, and deter-

mines what state a ready input (or multiple inputs) must be

before proceeding. The GPIF vector can be programmed to

advance a FIFO to the next data value, advance an address,

etc. A sequence of the GPIF vectors make up a single

waveform that will be executed to perform the desired data

move between the FX2LP and the external device.

3.14.1

The 100- and 128-pin packages bring out all six Control Output

pins (CTL0-CTL5). The 8051 programs the GPIF unit to define

the CTL waveforms. The 56-pin package brings out three of

these signals, CTL0–CTL2. CTLx waveform edges can be

programmed to make transitions as fast as once per clock

(20.8 ns using a 48-MHz clock).

3.14.2

The 100- and 128-pin packages bring out all six Ready inputs

(RDY0–RDY5). The 8051 programs the GPIF unit to test the

RDY pins for GPIF branching. The 56-pin package brings out

two of these signals, RDY0–1.

3.14.3

Nine GPIF address lines are available in the 100- and 128-pin

packages, GPIFADR[8..0]. The GPIF address lines allow

indexing through up to a 512-byte block of RAM. If more

address lines are needed, I/O port pins can be used.

3.14.4

In master mode, the 8051 appropriately sets GPIF transaction

count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or

GPIFTCB0) for unattended transfers of up to 2

The GPIF automatically throttles data flow to prevent under or

overflow until the full number of requested transactions

complete. The GPIF decrements the value in these registers

to represent the current status of the transaction.

GPIF and FIFO Clock Rates

GPIF

Six Control OUT Signals

Six Ready IN Signals

Nine GPIF Address OUT Signals

Long Transfer Mode

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

32

Page 11 of 60

transactions.