CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 7

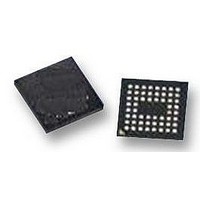

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

Table 3-5. Reset Timing Values

3.9.2

The 8051 puts itself and the rest of the chip into a power-down

mode by setting PCON.0 = 1. This stops the oscillator and

PLL. When WAKEUP is asserted by external logic, the oscil-

lator restarts, after the PLL stabilizes, and then the 8051

receives a wakeup interrupt. This applies whether or not

FX2LP is connected to the USB.

The FX2LP exits the power-down (USB suspend) state using

one of the following methods:

The second wakeup pin, WU2, can also be configured as a

general purpose I/O pin. This allows a simple external R-C

network to be used as a periodic wakeup source. Note that

WAKEUP is by default active LOW.

Power-on Reset with crystal

Power-on Reset with external

clock

Powered Reset

• USB bus activity (if D+/D– lines are left floating, noise on

• External logic asserts the WAKEUP pin

• External logic asserts the PA3/WU2 pin.

these lines may indicate activity to the FX2LP and initiate a

wakeup).

RESET#

VCC

Wakeup Pins

Condition

T

Power on Reset

RESET

200 ∝s + Clock stability time

T

200 ∝s

5 ms

RESET

Figure 3-2. Reset Timing Plots

3.3V

V

3.0V

0V

IL

RESET#

3.10

3.10.1

The FX2LP has 16 KBytes of internal program/data RAM,

where PSEN#/RD# signals are internally ORed to allow the

8051 to access it as both program and data memory. No USB

control registers appear in this space.

Two memory maps are shown in the following diagrams:

Figure 3-3 Internal Code Memory, EA = 0

Figure 3-4 External Code Memory, EA = 1.

3.10.2

This mode implements the internal 16-KByte block of RAM

(starting at 0) as combined code and data memory. When

external RAM or ROM is added, the external read and write

strobes are suppressed for memory spaces that exist inside

the chip. This allows the user to connect a 64-KByte memory

without requiring address decodes to keep clear of internal

memory spaces.

Only the internal 16 KBytes and scratch pad 0.5 KBytes RAM

spaces have the following access:

3.10.3

The bottom 16 KBytes of program memory is external, and

therefore the bottom 16 KBytes of internal RAM is accessible

only as data memory.

VCC

• USB download

• USB upload

• Set-up data pointer

• I

2

C interface boot load.

Program/Data RAM

Size

Internal Code Memory, EA = 0

External Code Memory, EA = 1

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

T

RESET

Powered Reset

V

3.3V

0V

IL

Page 7 of 60