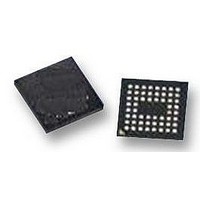

CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 12

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Document #: 38-08032 Rev. *K

3.15

The EZ-USB can calculate ECCs (Error-Correcting Codes) on

data that passes across its GPIF or Slave FIFO interfaces.

There are two ECC configurations: Two ECCs, each calcu-

lated over 256 bytes (SmartMedia Standard); and one ECC

calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit

error.

3.15.1

The two ECC configurations are selected by the ECCM bit:

3.15.1.1 ECCM = 0

Two 3-byte ECCs, each calculated over a 256-byte block of

data. This configuration conforms to the SmartMedia

Standard.

Write any value to ECCRESET, then pass data across the

GPIF or Slave FIFO interface. The ECC for the first 256 bytes

of data will be calculated and stored in ECC1. The ECC for the

next 256 bytes will be stored in ECC2. After the second ECC

is calculated, the values in the ECCx registers will not change

until ECCRESET is written again, even if more data is subse-

quently passed across the interface.

3.15.1.2 ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

Write any value to ECCRESET then pass data across the

GPIF or Slave FIFO interface. The ECC for the first 512 bytes

of data will be calculated and stored in ECC1; ECC2 is unused.

After the ECC is calculated, the value in ECC1 will not change

until ECCRESET is written again, even if more data is subse-

quently passed across the interface

3.16

The core has the ability to directly edit the data contents of the

internal 16-KByte RAM and of the internal 512-byte scratch

pad RAM via a vendor-specific command. This capability is

normally used when “soft” downloading user code and is

available only to and from internal RAM, only when the 8051

is held in reset. The available RAM spaces are 16 KBytes from

0x0000–0x3FFF

0xE000–0xE1FF (scratch pad data RAM).

3.17

FX2LP provides two identical autopointers. They are similar to

the internal 8051 data pointers, but with an additional feature:

they can optionally increment after every memory access. This

capability is available to and from both internal and external

RAM. The autopointers are available in external FX2LP

registers, under control of a mode bit (AUTOPTRSET-UP.0).

Using the external FX2LP autopointer access (at 0xE67B –

0xE67C) allows the autopointer to access all RAM, internal

and external to the part. Also, the autopointers can point to any

FX2LP register or endpoint buffer space. When autopointer

access to external memory is enabled, location 0xE67B and

0xE67C in XDATA and code space cannot be used.

Notes:

7.

8.

9.

To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

After the data has been downloaded from the host, a “loader” can execute from internal RAM in order to transfer downloaded data to external memory.

This EEPROM does not have address pins.

ECC Implementation

ECC Generation

USB Uploads and Downloads

Autopointer Access

(code/data)

[7]

and

512

[8]

bytes

from

3.18

FX2LP has one I

controllers, one that automatically operates at boot time to

load VID/PID/DID and configuration information, and another

that the 8051, once running, uses to control external I

devices. The I

3.18.1

The I

resistors even if no EEPROM is connected to the FX2LP.

External EEPROM device address pins must be configured

properly. See Table 3-8 for configuring the device address

pins.

Table 3-8. Strap Boot EEPROM Address Lines to These

Values

3.18.2

At power-on reset the I

VID/PID/DID configuration bytes and up to 16 KBytes of

program/data. The available RAM spaces are 16 KBytes from

0x0000–0x3FFF and 512 bytes from 0xE000–0xE1FF. The

8051 will be in reset. I

power-on reset.

3.18.3

The 8051 can control peripherals connected to the I

using the I2CTL and I2DAT registers. FX2LP provides I

master control only, it is never an I

3.19

EZ-USB FX2

The EZ-USB FX2LP is form/fit and with minor exceptions

functionally compatible with its predecessor, the EZ-USB FX2.

This makes for an easy transition for designers wanting to

upgrade their systems from the FX2 to the FX2LP. The pinout

and package selection are identical, and the vast majority of

firmware previously developed for the FX2 will function in the

FX2LP.

For designers migrating from the FX2 to the FX2LP a change

in the bill of material and review of the memory allocation (due

to increased internal memory) is required for more information

about migrating from EZ-USB FX2 to EZ-USB FX2LP, please

see further details in the application note titled Migrating from

EZ-USB FX2 to EZ-USB FX2LP, which is available on the

Cypress Website.

16

128

256

4K

8K

16K

Bytes

2

C pins SCL and SDA must have external 2.2-k. pull-up

I

I

I

I

Compatible with Previous Generation

2

2

2

2

C Port Pins

C Interface Boot Load Access

C Interface General-Purpose Access

C Controller

24LC00

24LC01

24LC02

24LC32

24LC64

24LC128

Example EEPROM

2

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

C port operates in master mode only.

2

[9]

C port that is driven by two internal

2

C interface boot loads only occur after

2

C interface boot loader will load the

2

C slave.

N/A

A2

0

0

0

0

0

N/A

Page 12 of 60

A1

0

0

0

0

0

2

N/A

A0

C bus

0

0

1

1

1

2

2

C

C