EP4SGX290KF40C3N Altera, EP4SGX290KF40C3N Datasheet - Page 586

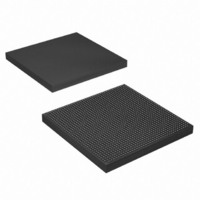

EP4SGX290KF40C3N

Manufacturer Part Number

EP4SGX290KF40C3N

Description

IC STRATIX IV GX 290K 1517FBGA

Manufacturer

Altera

Series

Stratix® IV GXr

Datasheets

1.EP4SGX110DF29C3N.pdf

(80 pages)

2.EP4SGX110DF29C3N.pdf

(1154 pages)

3.EP4SGX110DF29C3N.pdf

(432 pages)

4.EP4SGX110DF29C3N.pdf

(22 pages)

5.EP4SGX110DF29C3N.pdf

(30 pages)

6.EP4SGX110DF29C3N.pdf

(72 pages)

Specifications of EP4SGX290KF40C3N

Number Of Logic Elements/cells

291200

Number Of Labs/clbs

11648

Total Ram Bits

17248

Number Of I /o

744

Voltage - Supply

0.87 V ~ 0.93 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1517-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-2624

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- EP4SGX110DF29C3N PDF datasheet

- EP4SGX110DF29C3N PDF datasheet #2

- EP4SGX110DF29C3N PDF datasheet #3

- EP4SGX110DF29C3N PDF datasheet #4

- EP4SGX110DF29C3N PDF datasheet #5

- EP4SGX110DF29C3N PDF datasheet #6

- Current page: 586 of 1154

- Download datasheet (32Mb)

1–142

Stratix IV Device Handbook Volume 2: Transceivers

1

1

The rateswitch signal serves as the input signal to the PCIe rateswitch controller.

After seeing a transition on the rateswitch signal from the PHY-MAC layer, the PCIe

rateswitch controller performs the following operations:

■

■

■

PCIe rateswitch controller location:

■

■

■

When operating at the Gen 2 data rate, asserting the rx_digitalreset signal causes

the PCIe rateswitch circuitry to switch the transceiver to Gen 1 data rate.

When switching from Gen1 to Gen2 using the dynamic reconfiguration controller,

you must set the two ports of the dynamic reconfiguration controller, tx_preemp_0t

and tx_preemp_2t, to zero to meet the Gen2 de-emphasis specifications. When

switching from Gen2 to Gen1, if your system requires specific settings on

tx_preemp_01 and tx_preemp_2t, those values must be set at the respective two ports

of the dynamic reconfiguration controller to meet your system requirements.

When the PHY-MAC layer instructs a rateswitch between the Gen1 (2.5 Gbps) and

Gen2 (5 Gbps) signaling rates, both the transmitter high-speed serial and low-speed

parallel clock and the CDR recovered clock must switch to support the instructed data

rate. Stratix IV GX and GT transceivers have dedicated PCIe clock switch circuitry

located in the following blocks:

■

■

■

Controls the PCIe clock switch circuitry to switch between Gen1 (2.5 Gbps) and

Gen2 (5 Gbps) signaling rate depending on the rateswitch signal level

Disables and resets the transmitter and receiver phase compensation FIFO

pointers until the PCIe clock switchover circuitry indicates successful rateswitch

completion

Communicates completion of rateswitch to the PCIe interface module, which in

turn communicates completion of the rateswitch to the PHY-MAC layer on the

pipephydonestatus signal

In PCIe ×1 mode, the PCIe rateswitch controller is located in the transceiver PCS of

each channel.

In PCIe ×4 mode, the PCIe rateswitch controller is located in CMU0_Channel within

the transceiver block.

In PCIe ×8 mode, the PCIe rateswitch controller is located in CMU0_Channel within

the master transceiver block.

Local clock divider in transmitter PMA of each transceiver channel

CMU0 clock divider in CMU0_Channel of each transceiver block

Receiver CDR in receiver PMA of each transceiver channel

PCIe Rateswitch Controller

PCIe Clock Switch Circuitry

Chapter 1: Transceiver Architecture in Stratix IV Devices

February 2011 Altera Corporation

Transceiver Block Architecture

Related parts for EP4SGX290KF40C3N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: