DF2218BR24V Renesas Electronics America, DF2218BR24V Datasheet - Page 624

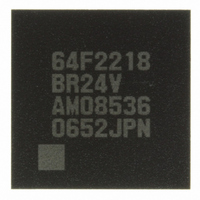

DF2218BR24V

Manufacturer Part Number

DF2218BR24V

Description

IC H8S/2218 MCU FLASH 112-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Specifications of DF2218BR24V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

24MHz

Connectivity

SCI, SmartCard, USB

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

69

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 6x10b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

112-LFBGA

For Use With

HS0005KCU11H - EMULATOR E10A-USB H8S(X),SH2(A)3DK2218-SS - KIT DEV H8S/2218 WINDOWS SIDESHW3DK2218 - DEV EVAL KIT H8S/2218

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2218BR24V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 624 of 758

- Download datasheet (5Mb)

Table 17.4 shows the boot mode operations between reset end and branching to the programming

control program.

1. When boot mode is used, the flash memory programming control program must be prepared in

2. The SCI_2 should be set to asynchronous mode, and the transfer format as follows: 8-bit data,

3. When the boot program is initiated, the chip measures the low-level period of asynchronous

4. After matching the bit rates, the chip transmits one H'00 byte to the host to indicate the end of

Rev.7.00 Dec. 24, 2008 Page 568 of 698

REJ09B0074-0700

the host beforehand. Prepare a programming control program in accordance with the

description in section 17.8, Flash Memory Programming/Erasing. In boot mode, if any data has

been programmed into the flash memory (if all data is not 1), all flash memory blocks are

erased. Boot mode is for use in enforced exit when user program mode is unavailable, such as

the first time on-board programming is performed, or if the program activated in user program

mode is accidentally erased.

1 stop bit, and no parity.

SCI communication data (H'00) transmitted continuously from the host. The chip then

calculates the bit rate of transmission from the host, and adjusts the SCI_2 bit rate to match that

of the host. The reset should end with the RxD pin high. The RxD and TxD pins should be

pulled up on the board if necessary. After the reset ends, it takes approximately 100 states

before the chip is ready to measure the low-level period.

bit rate adjustment. The host should confirm that this adjustment end indication (H'00) has

been received normally, and transmit one H'55 byte to the chip. If reception could not be

performed normally, initiate boot mode again by a reset. Depending on the host’s transfer bit

rate and system clock frequency of this LSI, there will be a discrepancy between the bit rates of

the host and the chip. To operate the SCI properly, set the host’s transfer bit rate and system

clock frequency of this LSI within the ranges listed in table 17.5.

Legend:

× : Don ’ t care

Note: * Mode pin and FWE pin input must satisfy the mode programming setup time (t

with respect to the reset release timing.

Host

Figure 17.8 System Configuration in SCI Boot Mode

Verify data transmission

Write data reception

01×

0

1

EMLE

FWE

MD2 to MD0*

RxD2

TxD2

SCI_2

This LSI

Flash memory

On-chip RAM

MDS

= 200ns)

Related parts for DF2218BR24V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: