Z8F64220100ZDA Zilog, Z8F64220100ZDA Datasheet - Page 165

Z8F64220100ZDA

Manufacturer Part Number

Z8F64220100ZDA

Description

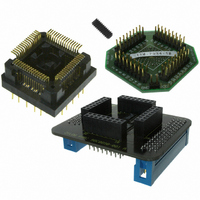

ADAPTER ICE Z8 ENCORE 64K 64LQFP

Manufacturer

Zilog

Specifications of Z8F64220100ZDA

Module/board Type

*

For Use With/related Products

Z8 Encore!™

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3403

- Current page: 165 of 297

- Download datasheet (9Mb)

PS019921-0308

Follow the steps below for the data transfer for a read operation to a 10-bit addressed

slave:

1. Software writes

2. Software asserts the START and TXI bits of the I

3. The I

4. The I

5. After the first bit has been shifted out, a Transmit interrupt is asserted.

6. Software responds by writing the lower eight bits of address to the I

7. The I

8. If the I

9. The I

10. The I

11. Software responds by setting the START bit of the I

12. Software responds by writing 11110B followed by the 2-bit slave address and a 1

13. If only one byte is to be read, software sets the NAK bit of the I

14. After the I

Data register.

register.

during the next high period of SCL, the I

Status register. Continue with

If the slave does not acknowledge the first address byte, the I

NCKI bit and clears the ACK bit in the I

Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI

bit. The I

NCKI bits. The transaction is complete (ignore following steps).

register (second address byte).

I

repeated START and by clearing the TXI bit.

(read) to the I

acknowledge by pulling the SDA signal low during the next high period of SCL, the

I

If the slave does not acknowledge the second address byte, the I

NCKI bit and clears the ACK bit in the I

Not Acknowledge interrupt by setting the STOP and FLUSH bits and clearing the TXI

bit. The I

NCKI bits. The transaction is complete (ignore the following steps).

2

2

C Controller generates a Transmit interrupt.

C Controller sets the ACK bit in the I

2

2

2

2

2

C Controller sends the Start condition.

C Controller loads the I

C Controller completes shifting of the two address bits and a 0 (write).

C Controller loads the I

C Controller shifts out the second address byte. After the first bit is shifted, the

2

C slave acknowledges the first address byte by pulling the SDA signal low

2

2

C Controller sends the STOP condition on the bus and clears the STOP and

C Controller sends the STOP condition on the bus and clears the STOP and

2

C Controller shifts out the 2nd address byte, the I

2

C Data register.

11110B

followed by the two address bits and a 0 (write) to the I

2

2

step

C Shift register with the contents of the I

C Shift register with the contents of the I

9.

2

C Status register. Continue with

2

2

2

C Status register. Software responds to the

C Status register. Software responds to the

C Controller sets the ACK bit in the I

2

C Control register.

Z8 Encore! XP

2

C Control register to generate a

Product Specification

2

2

C slave sends an

C Controller sets the

2

2

C Controller sets the

C Control register.

®

2

C Data register.

F64XX Series

2

2

step

C Data

C Data

I2C Controller

15.

2

C

2

C

151

Related parts for Z8F64220100ZDA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: