Z8F64220100ZDA Zilog, Z8F64220100ZDA Datasheet - Page 176

Z8F64220100ZDA

Manufacturer Part Number

Z8F64220100ZDA

Description

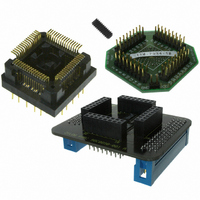

ADAPTER ICE Z8 ENCORE 64K 64LQFP

Manufacturer

Zilog

Specifications of Z8F64220100ZDA

Module/board Type

*

For Use With/related Products

Z8 Encore!™

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3403

- Current page: 176 of 297

- Download datasheet (9Mb)

PS019921-0308

DMA_ADC Operation

Configuring DMA_ADC for Data Transfer

3. Write the Start and End Register File address high nibbles to the DMAx End/Start

4. Write the lower byte of the Start Address to the DMAx Start/Current Address register.

5. Write the lower byte of the End Address to the DMAx End Address register.

6. Write to the DMAx Control register to complete the following:

DMA_ADC transfers data from the ADC to the Register File. The sequence of operations

in a DMA_ADC data transfer is:

1. ADC completes conversion on the current ADC input channel and signals the DMA

2. DMA_ADC requests control of the system bus (address and data) from the eZ8 CPU.

3. After the eZ8 CPU acknowledges the bus request, DMA_ADC transfers the two-byte

4. If the current ADC Analog Input is the highest numbered input to be converted:

Follow the steps below to configure and enable DMA_ADC:

1. Write the DMA_ADC Address register with the 7 most-significant bits of the Register

2. Write to the DMA_ADC Control register to complete the following:

Address High Nibble register.

–

–

–

–

–

–

controller that two-bytes of ADC data are ready for transfer.

ADC output value to the Register File and then returns system bus control back to the

eZ8 CPU.

–

–

If the current ADC Analog Input is not the highest numbered input to be converted,

DMA_ADC initiates data conversion in the next higher numbered ADC Analog Input.

File address for data transfers.

Select loop or single-pass mode operation

Select the data transfer direction (either from the Register File RAM to the on-

chip peripheral control register; or from the on-chip peripheral control register to

the Register File RAM)

Enable the DMAx interrupt request, if desired

Select Word or Byte mode

Select the DMAx request trigger

Enable the DMAx channel

DMA_ADC resets the ADC Analog Input number to 0 and initiates data

conversion on ADC Analog Input 0.

If configured to generate an interrupt, DMA_ADC sends an interrupt request to

the Interrupt Controller

Z8 Encore! XP

Direct Memory Access Controller

Product Specification

®

F64XX Series

162

Related parts for Z8F64220100ZDA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: