Z8F64220100ZDA Zilog, Z8F64220100ZDA Datasheet - Page 50

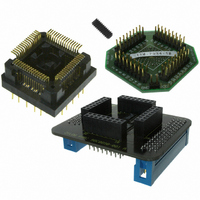

Z8F64220100ZDA

Manufacturer Part Number

Z8F64220100ZDA

Description

ADAPTER ICE Z8 ENCORE 64K 64LQFP

Manufacturer

Zilog

Specifications of Z8F64220100ZDA

Module/board Type

*

For Use With/related Products

Z8 Encore!™

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3403

- Current page: 50 of 297

- Download datasheet (9Mb)

DMA0 Control

DMA0CTL (FB0H - Read/Write)

DMA0 I/O Address

DMA0IO (FB1H - Read/Write)

PS019921-0308

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

Request Trigger Source Select

000 = Timer 0

001 = Timer 1

010 = Timer 2

011 = Timer 3

100 = UART0 Received Data

register

101 = UART1 Received Data

register

110 = I2C receiver contains valid

data

111 = Reserved

Word Select

0 = DMA transfers 1 byte per

request

1 = DMA transfers 2 bytes per

request

DMA0 Interrupt Enable

0 = DMA0 does not generate

interrupts

1 = DMA0 generates an interrupt

when

DMA0 Data Transfer Direction

0 = Register File to peripheral

registers

1 = Peripheral registers to Register

File

DMA0 Loop Enable

0 = DMA disables after End Address

1 = DMA reloads Start Address after

run

DMA0 Enable

0 = DMA0 is disabled

1 = DMA0 is enabled

DMA0 Peripheral Register Address

control

Low byte of on-chip peripheral

registers on Register File page FH

End Address data is transferred

End Address and continues to

contains valid data

contains valid data

DMA0 Address High Nibble

DMA0H (FB2H - Read/Write)

DMA0 Start/Current Address Low Byte

DMA0START (FB3H - Read/Write)

DMA0 End Address Low Byte

DMA0END (FB4H - Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0

Z8 Encore! XP

DMA0 Start Address [11:8]

DMA0 End Address [11:8]

DMA0 Start Address [7:0]

DMA0 End Address [7:0]

Product Specification

Control Register Summary

®

F64XX Series

36

Related parts for Z8F64220100ZDA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: