Z8F64220100ZDA Zilog, Z8F64220100ZDA Datasheet - Page 156

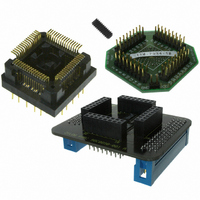

Z8F64220100ZDA

Manufacturer Part Number

Z8F64220100ZDA

Description

ADAPTER ICE Z8 ENCORE 64K 64LQFP

Manufacturer

Zilog

Specifications of Z8F64220100ZDA

Module/board Type

*

For Use With/related Products

Z8 Encore!™

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3403

- Current page: 156 of 297

- Download datasheet (9Mb)

PS019921-0308

Note:

Software Control of I

Caution:

Writing to the I

the I

shifting out until the Data register is written with the next value to send or the STOP or

START bits are set indicating the current byte is the last one to send.

Transmit interrupts occur when the TDRE bit of the I

bit in the I

tions when the transmit data register is empty:

•

•

•

•

The fourth interrupt source is the baud rate generator. If the I

(IEN bit in the I2CCTL register = 0) and the BIRQ bit in the I2CCTL register = 1, an inter-

rupt is generated when the baud rate generator counts down to 1. This allows the I

rate generator to be used by software as a general purpose timer when IEN = 0.

Software can control I

I

To use interrupts, the I

in the I

To control transactions by polling, the interrupt bits (TDRE, RDRF and NCKI) in the I

Status register should be polled. The TDRE bit asserts regardless of the state of the TXI

bit.

Either or both transmit and receive data movement can be controlled by the DMA

Controller. The DMA Controller channel(s) must be initialized to select the I

and receive requests. Transmit DMA requests require that the TXI bit in the I

register be set.

2

C Status register or by DMA. Note that not all products include a DMA Controller.

2

The I

The first bit of the byte of an address is shifting out and the RD bit of the I

register is deasserted.

The first bit of a 10-bit address shifts out.

The first bit of write data shifts out.

Acknowledge before the last byte has been sent. After receiving the Not

Acknowledge, the I

pauses until either the STOP or START bits in the Control register are set.

A transmit (write) DMA operation hangs if the slave responds with a Not

C Controller pauses at the beginning of the Acknowledge cycle of the byte currently

2

C Control register must be set to enable transmit interrupts.

2

2

C Controller is enabled.

C Control register is set. Transmit interrupts occur under the following condi-

2

C Data register always clears the TRDE bit to 0. When TDRE is asserted,

2

C Transactions

2

2

C transactions by using the I

C interrupt must be enabled in the Interrupt Controller. The TXI bit

2

C Controller sets the NCKI bit in the Status register and

2

C Controller interrupt, by polling the

2

C Status register sets and the TXI

Z8 Encore! XP

2

C Controller is disabled

Product Specification

®

F64XX Series

2

2

I2C Controller

C transmit

2

C Control

C Status

2

C baud

2

C

142

Related parts for Z8F64220100ZDA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: