Z8F64220100ZDA Zilog, Z8F64220100ZDA Datasheet - Page 160

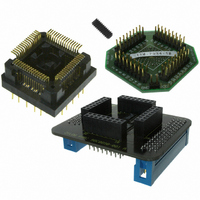

Z8F64220100ZDA

Manufacturer Part Number

Z8F64220100ZDA

Description

ADAPTER ICE Z8 ENCORE 64K 64LQFP

Manufacturer

Zilog

Specifications of Z8F64220100ZDA

Module/board Type

*

For Use With/related Products

Z8 Encore!™

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3403

- Current page: 160 of 297

- Download datasheet (9Mb)

PS019921-0308

Address Only Transaction with a 10-bit Address

13. The I

14. If more bytes remain to be sent, return to

15. Software responds by setting the STOP bit of the I

16. The I

17. The slave may either Acknowledge or Not Acknowledge the last byte. Because either

18. The I

In the situation where software wants to determine if a slave with a 10-bit address is

responding without sending or receiving data, a transaction can be done which only con-

sists of an address phase.

a slave with 10-bit address will acknowledge. As an example, this transaction can be used

after a ‘write’ has been done to a EEPROM to determine when the EEPROM completes its

internal write operation and is once again responding to I

not Acknowledge the transaction can be repeated until the slave is able to Acknowledge.

Follow the steps below for an address only transaction to a 10-bit addressed slave:

1. Software asserts the IEN bit in the I

2. Software asserts the TXI bit of the I

3. The I

4. Software responds to the TDRE interrupt by writing the first slave address byte. The

5. Software asserts the START bit of the I

6. The I

S

sent, the Transmit interrupt is asserted.

to initiate a new transaction). In the STOP case, software clears the TXI bit of the I

Control register at the same time.

the STOP or START bit is already set, the NCKI interrupt does not occur.

STOP or START bit is cleared.

least-significant bit must be 0 for the write operation.

Slave Address

Figure 29. 10-Bit Address Only Transaction Format

1st 7 bits

2

2

2

2

2

C Controller shifts the data out of using the SDA signal. After the first bit is

C Controller completes transmission of the data on the SDA signal.

C Controller sends the STOP (or RESTART) condition to the I

C interrupt asserts, because the I

C Controller sends the START condition to the I

W = 0 A/A

Figure 29

displays this ‘address only’ transaction to determine if

2

2

C Control register.

C Control register to enable Transmit interrupts.

2

2

Slave Address

C Data register is empty (TDRE = 1)

C Control register.

step

2nd Byte

9.

2

Z8 Encore! XP

C Control register (or START bit

2

C transactions. If the slave does

2

C slave.

Product Specification

A/A P

®

2

C bus. The

F64XX Series

I2C Controller

2

C

146

Related parts for Z8F64220100ZDA

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: