R8A77850ADBGV#RD0Z Renesas Electronics America, R8A77850ADBGV#RD0Z Datasheet - Page 1491

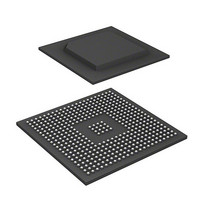

R8A77850ADBGV#RD0Z

Manufacturer Part Number

R8A77850ADBGV#RD0Z

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ADBGV#RD0Z

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R8A77850ADBGV#RD0ZR8A77850ADBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1491 of 1694

- Download datasheet (9Mb)

Notes: 1. If the data value is included in the match conditions, be sure to specify the operand

Bit

7, 6

5, 4

3

2, 1

0

2. If the quadword access is specified and the data value is included in the match

Bit Name

CD

ID

—

RW

CE

size.

conditions, the upper and lower 32 bits of 64-bit data are each compared with the

contents of both the match data setting register and the match data mask setting

register.

Initial

Value

All 0

All 0

0

All 0

0

R/W

R/W

R/W

R

R/W

R/W

Description

Bus Select

Specifies the bus to be included in the match conditions.

This bit is valid only when the operand access cycle is

specified as a match condition.

00: Operand bus for operand access

Others: Reserved (setting prohibited)

Instruction Fetch/Operand Access Select

Specifies the instruction fetch cycle or operand access

cycle as the match condition.

00: Instruction fetch cycle or operand access cycle

01: Instruction fetch cycle

10: Operand access cycle

11: Instruction fetch cycle or operand access cycle

Reserved

For read/write in this bit, refer to General Precautions on

Handling of Product.

Bus Command Select

Specifies the read/write cycle as the match condition.

This bit is valid only when the operand access cycle is

specified as a match condition.

00: Read cycle or write cycle

01: Read cycle

10: Write cycle

11: Read cycle or write cycle

Channel Enable

Validates/invalidates the channel. If this bit is 0, all the

other bits of this register are invalid.

0: Invalidates the channel.

1: Validates the channel.

Rev.1.00 Jan. 10, 2008 Page 1459 of 1658

29. User Break Controller (UBC)

REJ09B0261-0100

Related parts for R8A77850ADBGV#RD0Z

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: