MCIMX53-START Freescale Semiconductor, MCIMX53-START Datasheet - Page 9

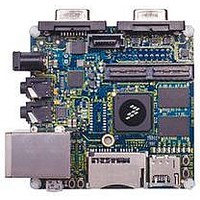

MCIMX53-START

Manufacturer Part Number

MCIMX53-START

Description

KIT DEVELOPMENT I.MX53

Manufacturer

Freescale Semiconductor

Series

i.MX53r

Type

MCUr

Datasheets

1.MCIMX53-START.pdf

(2 pages)

2.MCIMX53-START.pdf

(180 pages)

3.MCIMX53-START.pdf

(204 pages)

Specifications of MCIMX53-START

Contents

Board

Silicon Manufacturer

Freescale

Core Architecture

ARM

Core Sub-architecture

Cortex - A8

Silicon Core Number

I.MX5

Silicon Family Name

I.MX53

Peak Reflow Compatible (260 C)

Yes

Rohs Compliant

Yes

Leaded Process Compatible

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

i.MX53

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Freescale Semiconductor

Mnemonic

DEBUG

EXTMC

EPIT-1

EPIT-2

Block

ESAI

Debug System

External Memory

Controller

Enhanced

Periodic Interrupt

Timer

Enhanced Serial

Audio Interface

Block Name

i.MX53xA Automotive and Infotainment Applications Processors, Rev. 1

Table 2. i.MX53xA Digital and Analog Blocks (continued)

System

Control

Connectivity

Peripherals

Timer

Peripherals

Connectivity

Peripherals

Subsystem

The debug system provides real-time trace debug capability of both

instructions and data. It supports a trace protocol that is an integral part of

the ARM Real Time Debug solution (RealView).

Real-time tracing is controlled by specifying a set of triggering and filtering

resources, which include address and data comparators, three

cross-system triggers (CTI), counters, and sequencers.

debug access port (DAP) —The DAP provides real-time access for the

debugger without halting the core to system memory, peripheral register,

debug configuration registers and JTAG scan chains.

The EXTMC is an external and internal memory interface. It performs

arbitration between multi-AXI masters to multi-memory controllers, divided

into four major channels, fast memories (DDR2/DDR3/LPDDR2) channel,

slow memories (NOR-FLASH / PSRAM / NAND-FLASH etc.) channel,

internal memory (RAM, ROM) channel and graphical memory (GMEM)

channel.

In order to increase the bandwidth performance, the EXTMC separates the

buffering and the arbitration between different channels so parallel

accesses can occur. By separating the channels, slow accesses do not

interfere with fast accesses.

EXTMC Features:

Each EPIT is a 32-bit “set and forget” timer that starts counting after the

EPIT is enabled by software. It is capable of providing precise interrupts at

regular intervals with minimal processor intervention. It has a 12-bit

prescaler for division of input clock frequency to get the required time

setting for the interrupts to occur, and counter values can be programmed

on the fly.

The enhanced serial audio interface (ESAI) provides a full-duplex serial port

for serial communication with a variety of serial devices, including

industry-standard codecs, SPDIF transceivers, and other processors.

The ESAI consists of independent transmitter and receiver sections, each

section with its own clock generator.

The ESAI has 12 pins for data and clocking connection to external devices.

• 64-bit and 32-bit AXI ports

• Enhanced arbitration scheme for fast channel, including dynamic master

• Flexible bank interleaving

• Support 16/32-bit DDR2-800 or DDR3-800 or LPDDR2.

• Support up to 2 GByte DDR memories.

• Support NFC, EIM signal muxing scheme.

• Support 8/16/32-bit Nor-Flash/PSRAM memories (sync and async

• Support 4/8/14/16-bit ECC, page sizes of 512-B, 2-KB and 4-KB

• Multiple chip selects (up to 4).

• Enhanced DDR memory controller, supporting access latency hiding

• Support watermark for security (internal and external memories)

priority, and taking into account which pages are open or closed and

what type (read or write) was the last access

operating modes), at slow frequency. (8-bit is not supported on

D[23]-D[16]).

Nand-Flash (including MLC)

Brief Description

Modules List

9