MCIMX53-START Freescale Semiconductor, MCIMX53-START Datasheet - Page 14

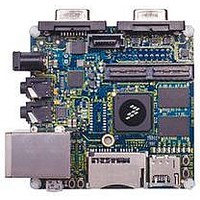

MCIMX53-START

Manufacturer Part Number

MCIMX53-START

Description

KIT DEVELOPMENT I.MX53

Manufacturer

Freescale Semiconductor

Series

i.MX53r

Type

MCUr

Datasheets

1.MCIMX53-START.pdf

(2 pages)

2.MCIMX53-START.pdf

(180 pages)

3.MCIMX53-START.pdf

(204 pages)

Specifications of MCIMX53-START

Contents

Board

Silicon Manufacturer

Freescale

Core Architecture

ARM

Core Sub-architecture

Cortex - A8

Silicon Core Number

I.MX5

Silicon Family Name

I.MX53

Peak Reflow Compatible (260 C)

Yes

Rohs Compliant

Yes

Leaded Process Compatible

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

i.MX53

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Modules List

14

Mnemonic

SECRAM

SPDIF

SDMA

Block

SPBA

SJC

Smart Direct

Memory Access

Secure /

Non-secure RAM

Secure JTAG

Interface

Shared

Peripheral Bus

Arbiter

Sony Philips

Digital Interface

Block Name

i.MX53xA Automotive and Infotainment Applications Processors, Rev. 1

Table 2. i.MX53xA Digital and Analog Blocks (continued)

System

Control

Peripherals

Internal

Memory

System

Control

Peripherals

System

Control

Peripherals

Multimedia

Peripherals

Subsystem

The SDMA is multi-channel flexible DMA engine. It helps in maximizing

system performance by off loading various cores in dynamic data routing.

The SDMA features list is as follows:

Secure / non-secure Internal RAM, controlled by SCC.

JTAG manipulation is a known hacker’s method of executing unauthorized

program code, getting control over secure applications, and running code in

privileged modes. The JTAG port provides a debug access to several

hardware blocks including the ARM processor and the system bus.

The JTAG port must be accessible during platform initial laboratory

bring-up, manufacturing tests and troubleshooting, as well as for software

debugging by authorized entities. However, in order to properly secure the

system, unauthorized JTAG usage should be strictly forbidden.

In order to prevent JTAG manipulation while allowing access for

manufacturing tests and software debugging, the i.MX53xA processor

incorporates a mechanism for regulating JTAG access. SJC provides four

different JTAG security modes that can be selected through an e-fuse

configuration.

SPBA (shared peripheral bus arbiter) is a two-to-one IP bus interface (IP

bus) arbiter.

A standard digital audio transmission protocol developed jointly by the Sony

and Philips corporations. Both transmitter and receiver functionalists are

supported.

• Powered by a 16-bit instruction-set micro-RISC engine

• Multi-channel DMA supports up to 32 time-division multiplexed DMA

• 48 events with total flexibility to trigger any combination of channels

• Memory accesses including linear, FIFO, and 2D addressing

• Shared peripherals between ARM and SDMA

• Very fast context-switching with two-level priority-based preemptive

• DMA units with auto-flush and prefetch capability

• Flexible address management for DMA transfers (increment, decrement,

• DMA ports can handle unidirectional and bidirectional flows (copy mode)

• Up to 8-word buffer for configurable burst transfers to / from the EXTMC

• Support of byte swapping and CRC calculations

• A library of scripts and API is available

channels

multi-tasking

and no address changes on source and destination address)

Brief Description

Freescale Semiconductor