MCIMX53-START Freescale Semiconductor, MCIMX53-START Datasheet - Page 31

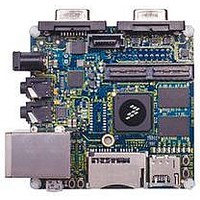

MCIMX53-START

Manufacturer Part Number

MCIMX53-START

Description

KIT DEVELOPMENT I.MX53

Manufacturer

Freescale Semiconductor

Series

i.MX53r

Type

MCUr

Datasheets

1.MCIMX53-START.pdf

(2 pages)

2.MCIMX53-START.pdf

(180 pages)

3.MCIMX53-START.pdf

(204 pages)

Specifications of MCIMX53-START

Contents

Board

Silicon Manufacturer

Freescale

Core Architecture

ARM

Core Sub-architecture

Cortex - A8

Silicon Core Number

I.MX5

Silicon Family Name

I.MX53

Peak Reflow Compatible (260 C)

Yes

Rohs Compliant

Yes

Leaded Process Compatible

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

i.MX53

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 31 of 180

- Download datasheet (2Mb)

1

2

3

1

2

4.3.2.3

The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008. The

parameters in

Freescale Semiconductor

DC input Low Voltage

Differential Input Logic High

Differential Input Logic Low

Input current (no pull-up/down)

240 Ohm unit calibration resolution

Keeper Circuit Resistance

Pull-up/Pull-down impedance Mismatch

High-level output voltage

Low-level output voltage

DC input Logic High

DC input Logic Low

Differential input Logic High

Differential input Logic Low

Over/undershoot peak

Over/undershoot area

(above OVDD or below OVSS)

Termination Voltage

Input current (no pull-up/down)

Pull-up/Pull-down impedance mismatch

240 Ω unit calibration resolution

Keeper Circuit Resistance

Note that the JEDEC LPDDR2 specification (JESD209_2B) supersedes any specification in this document.

The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as

the limitations for overshoot and undershoot.

Use an off-chip pull resistor of less than 60kΩ to override this keeper.

OVDD – I/O power supply (1.425 V–1.575 V for DDR3)

Vref – DDR3

Parameters

DDR3 Mode I/O DC Parameters

external reference voltage

Table 13

i.MX53xA Automotive and Infotainment Applications Processors, Rev. 1

Table 12. LPDDR2 I/O DC Electrical Parameters

are guaranteed per the operating ranges in

Table 13. DDR3 I/O DC Electrical Parameters

Vil(dc)

Vih(diff)

Vil(diff)

Iin

Symbol

VIH(diff)

VIL(diff)

VIH(dc)

VIL(dc)

Vpeak

Varea

Voh

Vol

Vtt

—

Iin

—

—

—

Minimum impedance

Vtt tracking OVDD/2

Test Conditions

VI=OVDD

VI = 0 V

configuration

VI=OVDD

VI = 0 V

—

—

—

—

—

—

—

—

—

—

—

—

See Note

OVSS

0.26

-15

0.49*OVDD

0.8*OVDD

Table

—

—

—

See Note

Vref

OVSS

Min

1

0.2

—

—

—

—

—

—

—

—

2

2

+0.1

(continued)

6, unless otherwise noted.

3

1

125

0.02

1.5

—

125

0.09

1.75

Vref

Typ

—

—

—

—

—

—

—

—

—

3

—

Electrical Characteristics

4

0.51*OVDD

Vref-0.13V

See Note

0.2*OVDD

See Note

Vref-0.1

OVDD

-0.26

12.8

290

+15

Max

0.67

-0.2

320

10

—

0.4

15

10

—

—

3

2

3

Unit

Ohm

V x

nS

nA

kΩ

kΩ

nA

Ω

Ω

V

V

V

V

V

V

V

V

%

V

31

Related parts for MCIMX53-START

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCIMX-LVDS1

Manufacturer:

Freescale Semiconductor

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: