DF2506BR26DV Renesas Electronics America, DF2506BR26DV Datasheet - Page 503

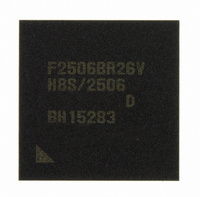

DF2506BR26DV

Manufacturer Part Number

DF2506BR26DV

Description

IC H8S/2506 MCU FLASH 176-LFBGA

Manufacturer

Renesas Electronics America

Series

H8® H8S/2500r

Specifications of DF2506BR26DV

Core Processor

H8S/2000

Core Size

16-Bit

Speed

26MHz

Connectivity

I²C, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

104

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

176-LFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2506BR26DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 503 of 980

- Download datasheet (6Mb)

Data transfer with other types of IC cards (direct convention and inverse convention) are

performed as described in the following.

With the direction convention type IC and the above sample start character, the logic 1 level

corresponds to state Z and the logic 0 level to state A, and transfer is performed in LSB-first order.

The start character data above is H'3B. For the direct convention type, clear the SDIR and SINV

bits in SCMR to 0. According to Smart Card regulations, clear the O/E bit in SMR to 0 to select

even parity mode.

With the inverse convention type, the logic 1 level corresponds to state A and the logic 0 level to

state Z, and transfer is performed in MSB-first order. The start character data for the above is

H'3F. For the inverse convention type, set the SDIR and SINV bits in SCMR to 1. According to

Smart Card regulations, even parity mode is the logic 0 level of the parity bit, and corresponds to

state Z. In this LSI, the SINV bit inverts only data bits D0 to D7. Therefore, set the O/E bit in

SMR to 1 to invert the parity bit for both transmission and reception.

13.7.3

Operation in block transfer mode is the same as that in the normal Smart Card interface mode,

except for the following points.

• In reception, though the parity check is performed, no error signal is output even if an error is

• In transmission, a guard time of at least 1 etu is left between the end of the parity bit and the

• In transmission, because retransmission is not performed, the TEND flag is set to 1, 11.5 etu

detected. However, the PER bit in SSR is set to 1 and must be cleared before receiving the

parity bit of the next frame.

start of the next frame.

after transmission start.

Block Transfer Mode

Figure 13.24 Inverse Convention (SDIR = SINV = O/E = 1)

Figure 13.23 Direct Convention (SDIR = SINV = O/E = 0)

(Z)

(Z)

Ds

Ds

A

A

D7

D0

Z

Z

D6

D1

Z

Z

D5

D2

A

A

D4

D3

A

Z

D3

D4

A

Z

D2

D5

A

Z

D1

D6

A

A

Section 13 Serial Communication Interface (SCI)

D0

D7

A

A

Rev. 6.00 Sep. 24, 2009 Page 455 of 928

Dp

Dp

Z

Z

(Z)

(Z)

State

State

REJ09B0099-0600

Related parts for DF2506BR26DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: