C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 248

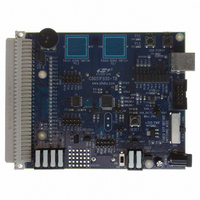

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 248 of 324

- Download datasheet (3Mb)

C8051F93x-C8051F92x

22.5.2. Read Sequence (Master)

During a read sequence, an SMBus master reads data from a slave device. The master in this transfer will

be a transmitter during the address byte, and a receiver during all data bytes. The SMBus interface

generates the START condition and transmits the first byte containing the address of the target slave and

the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then

received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more

bytes of serial data.

If hardware ACK generation is disabled, the ACKRQ is set to 1 and an interrupt is generated after each

received byte. Software must write the ACK bit at that time to ACK or NACK the received byte.

With hardware ACK generation enabled, the SMBus hardware will automatically generate the ACK/NACK,

and then post the interrupt. It is important to note that the appropriate ACK or NACK value should be

set up by the software prior to receiving the byte when hardware ACK generation is enabled.

Writing a 1 to the ACK bit generates an ACK; writing a 0 generates a NACK. Software should write a 0 to

the ACK bit for the last data transfer, to transmit a NACK. The interface exits Master Receiver Mode after

the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if

SMB0DAT is written while an active Master Receiver. Figure 22.6 shows a typical master read sequence.

Two received data bytes are shown, though any number of bytes may be received. The “data byte

transferred” interrupts occur at different places in the sequence, depending on whether hardware ACK

generation is enabled. The interrupt occurs before the ACK with hardware ACK generation disabled, and

after the ACK when hardware ACK generation is enabled.

248

S

Received by SMBus

Interface

Transmitted by

SMBus Interface

SLA

Figure 22.6. Typical Master Read Sequence

Interrupts with Hardware ACK Disabled (EHACK = 0)

Interrupts with Hardware ACK Enabled (EHACK = 1)

R

A

Data Byte

Rev. 1.1

A

S = START

P = STOP

A = ACK

N = NACK

R = READ

SLA = Slave Address

Data Byte

N

P

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc