C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 11

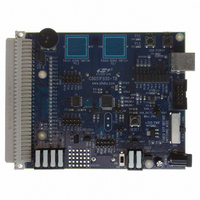

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 11 of 324

- Download datasheet (3Mb)

22. SMBus

23. UART0

24. Enhanced Serial Peripheral Interface (SPI0 and SPI1)

25. Timers

26. Programmable Counter Array

Figure 21.2. Port I/O Cell Block Diagram ............................................................... 213

Figure 21.3. Crossbar Priority Decoder with No Pins Skipped ............................... 217

Figure 21.4. Crossbar Priority Decoder with Crystal Pins Skipped ........................ 218

Figure 22.1. SMBus Block Diagram ....................................................................... 233

Figure 22.2. Typical SMBus Configuration ............................................................. 234

Figure 22.3. SMBus Transaction ............................................................................ 235

Figure 22.4. Typical SMBus SCL Generation......................................................... 238

Figure 22.5. Typical Master Write Sequence ......................................................... 247

Figure 22.6. Typical Master Read Sequence ......................................................... 248

Figure 22.7. Typical Slave Write Sequence ........................................................... 249

Figure 22.8. Typical Slave Read Sequence ........................................................... 250

Figure 23.1. UART0 Block Diagram ....................................................................... 255

Figure 23.2. UART0 Baud Rate Logic .................................................................... 256

Figure 23.3. UART Interconnect Diagram .............................................................. 257

Figure 23.4. 8-Bit UART Timing Diagram............................................................... 257

Figure 23.5. 9-Bit UART Timing Diagram............................................................... 258

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram .......................... 259

Figure 24.1. SPI Block Diagram ............................................................................. 263

Figure 24.2. Multiple-Master Mode Connection Diagram ....................................... 266

Figure 24.3. 3-Wire Single Master and 3-Wire Single Slave Mode

Figure 24.4. 4-Wire Single Master Mode and 4-Wire Slave Mode

Figure 24.5. Master Mode Data/Clock Timing ........................................................ 268

Figure 24.6. Slave Mode Data/Clock Timing (CKPHA = 0) .................................... 269

Figure 24.7. Slave Mode Data/Clock Timing (CKPHA = 1) .................................... 269

Figure 24.8. SPI Master Timing (CKPHA = 0)........................................................ 275

Figure 24.9. SPI Master Timing (CKPHA = 1)........................................................ 275

Figure 24.10. SPI Slave Timing (CKPHA = 0)........................................................ 276

Figure 24.11. SPI Slave Timing (CKPHA = 1)........................................................ 276

Figure 25.1. T0 Mode 0 Block Diagram.................................................................. 281

Figure 25.2. T0 Mode 2 Block Diagram.................................................................. 282

Figure 25.3. T0 Mode 3 Block Diagram.................................................................. 283

Figure 25.4. Timer 2 16-Bit Mode Block Diagram .................................................. 288

Figure 25.5. Timer 2 8-Bit Mode Block Diagram .................................................... 289

Figure 25.6. Timer 2 Capture Mode Block Diagram ............................................... 290

Figure 25.7. Timer 3 16-Bit Mode Block Diagram .................................................. 294

Figure 25.8. Timer 3 8-Bit Mode Block Diagram. ................................................... 295

Figure 25.9. Timer 3 Capture Mode Block Diagram ............................................... 296

Figure 26.1. PCA Block Diagram............................................................................ 300

Connection Diagram .............................................................................. 266

Connection Diagram .............................................................................. 266

Rev. 0.2

C8051F93x-C8051F92x

11

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc