C8051F930-TB Silicon Laboratories Inc, C8051F930-TB Datasheet - Page 127

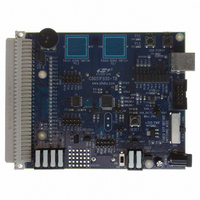

C8051F930-TB

Manufacturer Part Number

C8051F930-TB

Description

BOARD TARGET/PROTO W/C8051F930

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F930-TB

Contents

Board

Processor To Be Evaluated

C8051F930

Processor Series

C8051F9xx

Data Bus Width

8 bit

Interface Type

I2C, UART, SPI

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

0.9 V to 3.6 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

C8051F930

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1472

- Current page: 127 of 324

- Download datasheet (3Mb)

11.1. SFR Paging

To accommodate more than 128 SFRs in the 0x80 to 0xFF address space, SFR paging has been

implemented. By default, all SFR accesses target SFR Page 0x0 to allow access to the registers listed in

Table 11.1. During device initialization, some SFRs located on SFR Page 0xF may need to be accessed.

Table 11.2 lists the SFRs accessible from SFR Page 0x0F. Some SFRs are accessible from both pages,

including the SFRPAGE register. SFRs accessible only from Page 0xF are in bold .

The following procedure should be used when accessing SFRs from Page 0xF:

F8

F0

E8

E0

D8

D0

C8

C0

B8

B0

A8

A0

98

90

88

80

(bit addressable)

PSW

ACC

0(8)

P2

P1

P0

IE

Step 1. Save the current interrupt state (EA_save = EA).

Step 2. Disable Interrupts (EA = 0).

Step 3. Set SFRPAGE = 0xF.

Step 4. Access the SFRs located on SFR Page 0xF.

Step 5. Set SFRPAGE = 0x0.

Step 6. Restore interrupt state (EA = EA_save).

B

Table 11.2. Special Function Register (SFR) Memory Map (Page 0xF)

CRC0DAT

CLKSEL

1(9)

SP

ADC0PWR

CRC0CN

DPL

2(A)

CRC0IN

DPH

3(B)

Rev. 1.1

P0DRV

4(C)

C8051F93x-C8051F92x

CRC0FLIP

ADC0TK

P1DRV

TOFFL

5(D)

CRC0AUTO CRC0CNT

P2DRV

TOFFH

EIP1

EIE1

6(E)

SFRPAGE

PCON

EIP2

EIE2

7(F)

127

Related parts for C8051F930-TB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc