UPD17073 NEC, UPD17073 Datasheet - Page 126

UPD17073

Manufacturer Part Number

UPD17073

Description

4-BIT SINGLE-CHIP MICROCONTROLLER WITH HARDWARE FOR DIGITAL TUNING SYSTEM

Manufacturer

NEC

Datasheet

1.UPD17073.pdf

(226 pages)

- Current page: 126 of 226

- Download datasheet (2Mb)

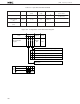

15. PLL FREQUENCY SYNTHESIZER

HF (High Frequency), and VHF (Very High Frequency) bands to a fixed frequency, by means of phase difference

comparison.

15.1 General

controlled oscillator (VCO), the PLL frequency synthesizer can be configured.

and outputs the phase difference between the signal and the reference frequency from the EO pin.

is disabled. For details of the PLL disable status, refer to 15.5 PLL Disable Status.

126

VCOH

VCOL

Note External circuit

Remarks 1. PLLMD1 and 0 (bits 1 and 0 of PLL mode select register. Refer to Figure 15-3) set the division

The PLL (Phase Locked Loop) frequency synthesizer is used to lock a frequency in the MF (Medium Frequency),

Figure 15-1 outlines the PLL frequency synthesizer. By connecting an external lowpass filter (LPF) and voltage

The PLL frequency synthesizer divides a signal input from the VCOH or VCOL pin by using a programmable divider,

However, the signal input from the VCOH pin is halved immediately before it is input to the programmable divider.

The PLL frequency synthesizer operates only while the CE pin is high. When the CE pin is low, the synthesizer

2. PLLRFCK2, 1, and 0 (bits 2-0 of PLL reference frequency select register. Refer to Figure 15-7) set

3. PLLUL (bit 0 of PLL unlock FF register. Refer to Figure 15-10) detects the status of the unlock FF.

Input selector

block

PLLMD1 flag

PLLMD0 flag

method of the PLL frequency synthesizer.

the reference frequency f

75 kHz

Figure 15-1. Outline of PLL Frequency Synthesizer

Reference frequ-

ency generator

PLLRFCK2 flag

PLLRFCK1 flag

PLLRFCK0 flag

Programmable

divider (PD)

r

of the PLL frequency synthesizer.

Phase comparator

( -DET)

PLLUL flag

Unlock FF

Charge

pump

Voltage-controlled

oscillator (VCO)

PD17072,17073

EO

Lowpass

filter (LPF)

Note

Note

Related parts for UPD17073

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

16/8 bit single-chip microcomputer

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

Dual audio power amp circuit

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

Dual comparator

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

MOS type composite field effect transistor

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

50 V/100 mA FET array incorporating 2 N-ch MOSFETs

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

6-pin small MM high-frequency double transistor

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

6-pin small MM high-frequency double transistor

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

6-pin small MM high-frequency double transistor

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

6-pin small MM high-frequency double transistor

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

Twin transistors equipped with different model chips(6P small MM)

Manufacturer:

NEC

Datasheet:

Part Number:

Description:

Bipolar analog integrated circuit

Manufacturer:

NEC

Datasheet: