ATTINY9-MAHR Atmel, ATTINY9-MAHR Datasheet - Page 28

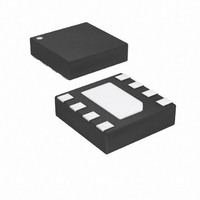

ATTINY9-MAHR

Manufacturer Part Number

ATTINY9-MAHR

Description

IC MCU AVR 1K FLASH 8UDFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Datasheet

1.ATTINY9-MAHR.pdf

(169 pages)

Specifications of ATTINY9-MAHR

Package / Case

8-UDFN Exposed Pad

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

12MHz

Number Of I /o

4

Core Processor

AVR

Program Memory Type

FLASH

Ram Size

32 x 8

Program Memory Size

1KB (1K x 8)

Oscillator Type

Internal

Peripherals

POR, PWM, WDT

Core Size

8-Bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Connectivity

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY9-MAHR

Manufacturer:

ST

Quantity:

101

- Current page: 28 of 169

- Download datasheet (5Mb)

8.2.1

8.2.2

28

ATtiny4/5/9/10

Power-on Reset

V

CC

Level Monitoring

A Power-on Reset (POR) pulse is generated by an on-chip detection circuit. The detection level

is defined in section

whenever V

Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the

Power-on Reset threshold voltage invokes the delay counter, which determines how long the

device is kept in reset after V

V

Figure 8-2.

Figure 8-3.

ATtiny4/5/9/10 have a V

V

VCC Level Monitoring Control and Status register” on page

The VLM circuit provides a status flag, VLMF, that indicates if voltage on the V

selected trigger level. The flag can be read from VLMCSR, but it is also possible to have an

interrupt generated when the VLMF status flag is set. This interrupt is enabled by the VLMIE bit

in the VLMCSR register. The flag can be cleared by changing the trigger level or by writing it to

zero. The flag is automatically cleared when the voltage at V

trigger level.

TIME-OUT

INTERNAL

TIME-OUT

INTERNAL

CC

CC

RESET

RESET

RESET

decreases below the detection level.

RESET

pin against fixed trigger levels. The trigger levels are set with VLM2:0 bits, see

V

V

CC

CC

CC

MCU Start-up, RESET Tied to V

MCU Start-up, RESET Extended Externally

is below the detection level. The POR circuit can be used to trigger the Start-up

“System and Reset Characteristics” on page

CC

V

V

POT

POT

Level Monitoring (VLM) circuit that compares the voltage level at the

CC

> t

t

TOUT

rise. The reset signal is activated again, without any delay, when

V

TOUT

RST

V

CC

RST

t

TOUT

34.

CC

rises back above the selected

120. The POR is activated

CC

pin is below the

8127D–AVR–02/10

“VLMCSR –

Related parts for ATTINY9-MAHR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 1KB FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 1KB FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 1K FLASH 8UDFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet: