DEMO9S08JM16 Freescale Semiconductor, DEMO9S08JM16 Datasheet - Page 311

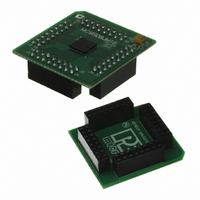

DEMO9S08JM16

Manufacturer Part Number

DEMO9S08JM16

Description

BOARD DEMO FOR JM16 FAMI

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08JM16.pdf

(47 pages)

2.DEMO9S08JM16.pdf

(5 pages)

3.DEMO9S08JM16.pdf

(4 pages)

4.DEMO9S08JM16.pdf

(386 pages)

Specifications of DEMO9S08JM16

Contents

Board with Daughter card, Cable, Documentation, Mini-AB USB Kit

Processor To Be Evaluated

MC9S08JM16

Data Bus Width

8 bit

Interface Type

USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

Flexis - S08JM

Rohs Compliant

Yes

For Use With/related Products

MC9S08JM16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- DEMO9S08JM16 PDF datasheet

- DEMO9S08JM16 PDF datasheet #2

- DEMO9S08JM16 PDF datasheet #3

- DEMO9S08JM16 PDF datasheet #4

- Current page: 311 of 386

- Download datasheet (8Mb)

17.4

This section describes the functional behavior of the USB module. It documents data packet processing

for endpoint 0 and data endpoints, USB suspend and resume states, SOF token processing, reset conditions

and interrupts.

17.4.1

Figure 17-2

following sections. The module involves several major blocks — USB transceiver (XCVR), USB serial

interface engine (SIE), a 3.3 V regulator (VREG), endpoint buffer manager, shared RAM arbitration, USB

RAM and the SkyBlue gasket.

17.4.1.1

The SIE is composed of two major functions: TX Logic and RX Logic. These major functions are

described below in more detail. The TX and RX logic are connected by a USB protocol engine which

manages packet flow to and from the USB module. The SIE is connected to the rest of the system via

Freescale Semiconductor

EPCTLDIS

EPSTALL

EPHSHK

Field

X

X

X

1

0

4

0

1

Functional Description

Block Descriptions

is the block diagram. The module’s sub-blocks and external signals are described in the

USB Serial Interface Engine (SIE)

Endpoint Stall — When set, this bit indicates that the endpoint is stalled. This bit has priority over all other

control bits in the endpoint control register, but is only valid if EPTXEN=1 or EPRXEN=1. Any access to this

endpoint will cause the USB module to return a STALL handshake. Once an endpoint is stalled it requires

intervention from the host controller.

0 Endpoint n is not stalled

1 Endpoint n is stalled

Endpoint Handshake — This bit determines if the endpoint will perform handshaking during a transaction

to the endpoint. This bit will generally be set unless the endpoint is isochronous.

0 No handshaking performed during a transaction to this endpoint (usually for isochronous endpoints)

1 Handshaking performed during a transaction to this endpoint

Bit Name

EPRXEN

3

0

0

1

1

1

Table 17-18. EPCTLn Field Descriptions (continued)

Table 17-19. Endpoint Enable/Direction Control

EPTXEN

2

0

1

0

1

1

MC9S08JM16 Series Data Sheet, Rev. 2

Disable endpoint

Enable endpoint for IN(TX) transfers only

Enable endpoint for OUT(RX) transfers only

Enable endpoint for IN, OUT and SETUP transfers.

RESERVED

Description

Endpoint Enable/Direction Control

Universal Serial Bus Device Controller (S08USBV1)

311

Related parts for DEMO9S08JM16

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: