DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 70

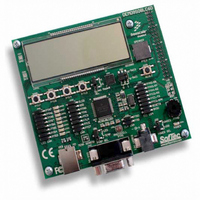

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 70 of 360

- Download datasheet (4Mb)

Chapter 5 Resets, Interrupts, and System Configuration

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control

value (RTIS) used to select one of seven wakeup periods. The RTI has a local interrupt enable, RTIE, to

allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to zeroes,

and no interrupts will be generated. See

Register

5.8

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space

are related to reset and interrupt systems.

Refer to the direct-page register summary in

address assignments for all registers. This section refers to registers and control bits only by their names.

A Freescale-provided equate or header file is used to translate these names into the appropriate absolute

addresses.

Some control bits in the SOPT1, SOPT2, and SPMSC2 registers are related to modes of operation.

Although brief descriptions of these bits are provided here, the related functions are discussed in greater

detail in

5.8.1

These bits are used to configure the IRQ function, report status, and acknowledge IRQ events.

70

IRQEDG

IRQPDD

Reset

Field

6

5

W

R

Chapter 3, “Modes of

(SRTISC)” for detailed information about this register.

Reset, Interrupt, and System Control Registers and Control Bits

Interrupt Pin Request Status and Control Register (IRQSC)

Interrupt Request (IRQ) Pull Device Disable— This read/write control bit is used to disable the internal

pullup/pulldown device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.

0 IRQ pull device enabled if IRQPE = 1.

1 IRQ pull device disabled if IRQPE = 1.

Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or

levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is

sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured

to detect rising edges, the optional pullup resistor is re-configured as an optional pulldown resistor.

0 IRQ is falling edge or falling edge/low-level sensitive.

1 IRQ is rising edge or rising edge/high-level sensitive.

0

0

7

Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

= Unimplemented or Reserved

IRQPDD

0

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Operation.”

IRQEDG

Table 5-3. IRQSC Field Descriptions

0

5

Section 5.8.7, “System Real-Time Interrupt Status and Control

Chapter 4,

IRQPE

0

4

Description

“Memory” of this data sheet for the absolute

IRQF

3

0

IRQACK

0

0

2

Freescale Semiconductor

IRQIE

0

1

IRQMOD

0

0

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: