DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 222

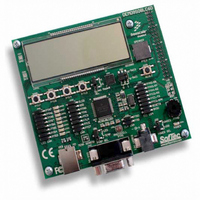

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 222 of 360

- Download datasheet (4Mb)

Chapter 12 Serial Communications Interface (S08SCIV3)

12.2.4

This register has eight read-only status flags. Writes have no effect. Special software sequences (which do

not involve writing to this register) are used to clear these status flags.

222

Reset

TDRE

Field

RWU

Field

SBK

RE

TC

2

1

0

7

6

W

R

TDRE

SCI Status Register 1 (SCIS1)

Receiver Enable — When the SCI receiver is off, the RxD pin reverts to being a general-purpose port I/O pin.

If LOOPS = 1, the RxD pin reverts to being a general-purpose I/O pin even if RE = 1.

0 Receiver off.

1 Receiver on.

Receiver Wakeup Control — This bit can be written to 1 to place the SCI receiver in a standby state where it

waits for automatic hardware detection of a selected wakeup condition. The wakeup condition is either an idle

line between messages (WAKE = 0, idle-line wakeup), or a logic 1 in the most significant data bit in a character

(WAKE = 1, address-mark wakeup). Application software sets RWU and (normally) a selected hardware

condition automatically clears RWU. Refer to

0 Normal SCI receiver operation.

1 SCI receiver in standby waiting for wakeup condition.

Send Break — Writing a 1 and then a 0 to SBK queues a break character in the transmit data stream. Additional

break characters of 10 or 11 bit times of logic 0 are queued as long as SBK = 1. Depending on the timing of the

set and clear of SBK relative to the information currently being transmitted, a second break character may be

queued before software clears SBK. Refer to

0 Normal transmitter operation.

1 Queue break character(s) to be sent.

Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from

the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read

SCIS1 with TDRE = 1 and then write to the SCI data register (SCID).

0 Transmit data register (buffer) full.

1 Transmit data register (buffer) empty.

Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break

character is being transmitted.

0 Transmitter active (sending data, a preamble, or a break).

1 Transmitter idle (transmission activity complete).

TC is cleared automatically by reading SCIS1 with TC = 1 and then doing one of the following three things:

1

7

• Write to the SCI data register (SCID) to transmit new data

• Queue a preamble by changing TE from 0 to 1

• Queue a break character by writing 1 to SBK in SCIC2

= Unimplemented or Reserved

Table 12-4. SCIC2 Register Field Descriptions (continued)

TC

1

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 12-5. SCIS1 Register Field Descriptions

Figure 12-9. SCI Status Register 1 (SCIS1)

RDRF

0

5

IDLE

Section 12.3.3.2, “Receiver Wakeup

Section 12.3.2.1, “Send Break and Queued

0

4

Description

Description

OR

3

0

NF

0

2

Operation,” for more details.

Freescale Semiconductor

FE

Idle,” for more details.

0

1

PF

0

0

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: