DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 103

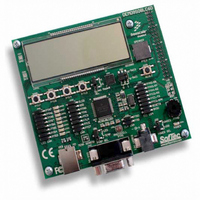

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 103 of 360

- Download datasheet (4Mb)

Chapter 8

Central Processor Unit (S08CPUV2)

8.1

This section provides summary information about the registers, addressing modes, and instruction set of

the CPU of the HCS08 Family. For a more detailed discussion, refer to the HCS08 Family Reference

Manual, volume 1, Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several

instructions and enhanced addressing modes were added to improve C compiler efficiency and to support

a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers

(MCU).

8.1.1

Features of the HCS08 CPU include:

Freescale Semiconductor

•

•

•

•

•

•

•

•

•

•

•

•

Object code fully upward-compatible with M68HC05 and M68HC08 Families

All registers and memory are mapped to a single 64-Kbyte address space

16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

16-bit index register (H:X) with powerful indexed addressing modes

8-bit accumulator (A)

Many instructions treat X as a second general-purpose 8-bit register

Seven addressing modes:

— Inherent — Operands in internal registers

— Relative — 8-bit signed offset to branch destination

— Immediate — Operand in next object code byte(s)

— Direct — Operand in memory at 0x0000–0x00FF

— Extended — Operand anywhere in 64-Kbyte address space

— Indexed relative to H:X — Five submodes including auto increment

— Indexed relative to SP — Improves C efficiency dramatically

Memory-to-memory data move instructions with four address mode combinations

Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on

the results of signed, unsigned, and binary-coded decimal (BCD) operations

Efficient bit manipulation instructions

Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

STOP and WAIT instructions to invoke low-power operating modes

Introduction

Features

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

103

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: