DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 291

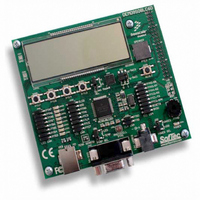

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 291 of 360

- Download datasheet (4Mb)

15.6.2.4

The ADC quantizes the ideal straight-line transfer function into 4096 steps (in 12-bit mode). Each step

ideally has the same height (1 code) and width. The width is defined as the delta between the transition

points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8, 10 or

12), defined as 1

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions

the code will transition when the voltage is at the midpoint between the points where the straight line

transfer function is exactly represented by the actual transfer function. Therefore, the quantization error

will be ± 1/2

conversion is only 1/2

For 12-bit conversions the code transitions only after the full code width is present, so the quantization

error is -1

15.6.2.5

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these

errors but the system should be aware of them because they affect overall accuracy. These errors are:

Freescale Semiconductor

•

•

•

•

•

•

•

Average the result by converting the analog input many times in succession and dividing the sum

of the results. Four samples are required to eliminate the effect of a 1

Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and

averaging. Noise that is synchronous to ADCK cannot be averaged out.

Zero-scale error (E

the actual code width of the first conversion and the ideal code width (1/2

modes and 1

the actual $001 code width and its ideal (1

Full-scale error (E

the last conversion and the ideal code width (1.5

mode). Note, if the last conversion is $3FE, then the difference between the actual $3FE code width

and its ideal (1

Differential non-linearity (DNL) — This error is defined as the worst-case difference between the

actual code width and the ideal code width for all conversions.

Integral non-linearity (INL) — This error is defined as the highest-value the (absolute value of the)

running sum of DNL achieves. More simply, this is the worst-case difference of the actual

transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

Total unadjusted error (TUE) — This error is defined as the difference between the actual transfer

function and the ideal straight-line transfer function, and therefore includes all forms of error.

LSB

LSB

Code Width and Quantization Error

Linearity Errors

to 0

LSB

in 8- or 10-bit mode. As a consequence, however, the code width of the first ($000)

LSB

LSB

, is:

LSB

and the code width of each step is 1

LSB

in 12-bit mode). Note, if the first conversion is $001, then the difference between

FS

) is used.

and the code width of the last ($FF or $3FF) is 1.5

ZS

) — This error is defined as the difference between the actual code width of

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

) (sometimes called offset) — This error is defined as the difference between

1

LSB

= (V

REFH

- V

LSB

REFL

) is used.

LSB

) / 2

LSB

N

in 8-bit or 10-bit modes and 1

.

Chapter 15 Analog-to-Digital Converter (S08ADC12V1)

LSB

LSB

, one-time error.

.

LSB

in 8-bit or 10-bit

LSB

in 12-bit

Eqn. 15-2

291

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: