DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 306

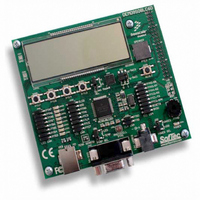

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 306 of 360

- Download datasheet (4Mb)

Chapter 17 Development Support

Figure 17-4

asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on

BKGD to the start of the bit time as perceived by the target MCU. The host initiates the bit time but the

target HCS08 finishes it. Because the target wants the host to receive a logic 0, it drives the BKGD pin low

for 13 BDC clock cycles, then briefly drives it high to speed up the rising edge. The host samples the bit

level about 10 cycles after starting the bit time.

306

SPEED-UP PULSE

PERCEIVED START

TO BKGD PIN

TARGET MCU

(TARGET MCU)

HOST DRIVE

DRIVE AND

BDC CLOCK

OF BIT TIME

BKGD PIN

shows the host receiving a logic 0 from the target HCS08 MCU. Because the host is

Figure 17-4. BDM Target-to-Host Serial Bit Timing (Logic 0)

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

10 CYCLES

HOST SAMPLES BKGD PIN

10 CYCLES

HIGH-IMPEDANCE

SPEEDUP

PULSE

EARLIEST START

OF NEXT BIT

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: