DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 286

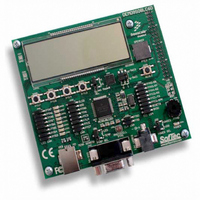

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 286 of 360

- Download datasheet (4Mb)

Chapter 15 Analog-to-Digital Converter (S08ADC12V1)

15.4.7.2

If ADACK is selected as the conversion clock, the ADC continues operation during stop3 mode. For

guaranteed ADC operation, the MCU’s voltage regulator must remain active during stop3 mode. Consult

the module introduction for configuration information for this MCU.

If a conversion is in progress when the MCU enters stop3 mode, it continues until completion. Conversions

can be initiated while the MCU is in stop3 mode by means of the hardware trigger or if continuous

conversions are enabled.

A conversion complete event sets the COCO and generates an ADC interrupt to wake the MCU from stop3

mode if the ADC interrupt is enabled (AIEN = 1).

15.4.8

The ADC module is automatically disabled when the MCU enters either stop1 or stop2 mode. All module

registers contain their reset values following exit from stop1 or stop2. Therefore the module must be

re-enabled and re-configured following exit from stop1 or stop2.

15.5

This section gives an example which provides some basic direction on how a user would initialize and

configure the ADC module. The user has the flexibility of choosing between configuring the module for

8-, 10-, or 12-bit resolution, single or continuous conversion, and a polled or interrupt approach, among

many other options. Refer to

15.5.1

15.5.1.1

Before the ADC module can be used to complete conversions, an initialization procedure must be

performed. A typical sequence is as follows:

286

1. Update the configuration register (ADCCFG) to select the input clock source and the divide ratio

used to generate the internal clock, ADCK. This register is also used for selecting sample time and

low-power configuration.

Initialization Information

MCU Stop1 and Stop2 Mode Operation

ADC Module Initialization Example

Stop3 Mode With ADACK Enabled

Initialization Sequence

It is possible for the ADC module to wake the system from low power stop

and cause the MCU to begin consuming run-level currents without

generating a system level interrupt. To prevent this scenario, software

should ensure that the data transfer blocking mechanism (discussed in

Section 15.4.4.2, “Completing

and continuing ADC conversions.

Hexadecimal values designated by a preceding 0x, binary values designated

by a preceding %, and decimal values have no preceding character.

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table

15-6,

Table

Conversions) is cleared when entering stop3

15-7, and

NOTE

NOTE

Table 15-8

for information used in this example.

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: