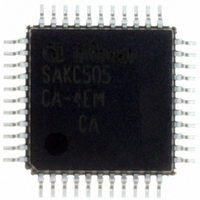

SAK-C505CA-4EM CA Infineon Technologies, SAK-C505CA-4EM CA Datasheet - Page 59

SAK-C505CA-4EM CA

Manufacturer Part Number

SAK-C505CA-4EM CA

Description

IC MCU 8BIT 32KB OTP MQFP-44-2

Manufacturer

Infineon Technologies

Series

C5xx/C8xxr

Datasheet

1.SAK-C505CA-4EM_CA.pdf

(88 pages)

Specifications of SAK-C505CA-4EM CA

Core Processor

C500

Core Size

8-Bit

Speed

20MHz

Connectivity

CAN, EBI/EMI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

34

Program Memory Size

32KB (32K x 8)

Program Memory Type

OTP

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

4.25 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 125°C

Package / Case

44-BQFP

Data Bus Width

8 bit

Data Ram Size

1.25 KB

Interface Type

CAN, USART

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

34

Number Of Timers

3

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

Packages

PG-MQFP-44

Max Clock Frequency

20.0 MHz

Sram (incl. Cache)

1.25 KByte

Can Nodes

1

A / D Input Lines (incl. Fadc)

8

Program Memory

32.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

K505CA4EMCANP

K505CA4EMCAXT

SAK-C505CA-4EMCA

SAK-C505CA-4EMCAINTR

SAK-C505CA-4EMCATR

SAK-C505CA-4EMCATR

SAKC505CA4EMCAXT

SP000106397

K505CA4EMCAXT

SAK-C505CA-4EMCA

SAK-C505CA-4EMCAINTR

SAK-C505CA-4EMCATR

SAK-C505CA-4EMCATR

SAKC505CA4EMCAXT

SP000106397

Table 12

Access Modes Selection

Access Mode

Program OTP memory byte

Read OTP memory byte

Program OTP lock bits

Read OTP lock bits

Read OTP version byte

Lock Bits Programming / Read

The C505A-4E/C505CA-4E has two programmable lock bits which, when programmed according

to

lock bits can also be read.

Table 13

Lock Bit Protection Types

Lock Bits at D1,D0

Data Sheet

D1

1

1

0

0

Table

13, provide four levels of protection for the on-chip OTP code memory. The state of the

D0

1

0

1

0

Protection

Level

Level 0

Level 1

Level 2

Level 3

EA/

V

V

V

V

V

V

PP

PP

PP

IH

IH

IH

Protection Type

The OTP lock feature is disabled. During normal operation of

the C505A-4E/C505CA-4E, the state of the EA pin is not

latched on reset.

During normal operation of the C505A-4E/C505CA-4E, MOVC

instructions executed from external program memory are

disabled from fetching code bytes from internal memory. EA is

sampled and latched on reset. An OTP memory read operation

is only possible using the ROM/OTP verification mode 2 for

protection level 1. Further programming of the OTP memory is

disabled (reprogramming security).

Same as level 1, but also OTP memory read operation using

OTP verification mode is disabled.

Same as level 2; but additionally external code execution by

setting EA=low during normal operation of the C505A-4E/

C505CA-4E is no more possible.

External code execution, which is initiated by an internal

program (e.g. by an internal jump instruction above the ROM

boundary), is still possible.

PROG

H

H

H

55

PRD

H

H

1

H

H

L

PMSEL

C505/C505C/C505A/C505CA

0

H

L

H

of sign. byte

Byte addr.

Address

(Port 2)

A8-14

A0-7

–

D1,D0 see

Table 13

(Port 0)

Data

D0-7

D0-7

12.00