SSTUB32865ET/G,518 NXP Semiconductors, SSTUB32865ET/G,518 Datasheet - Page 2

SSTUB32865ET/G,518

Manufacturer Part Number

SSTUB32865ET/G,518

Description

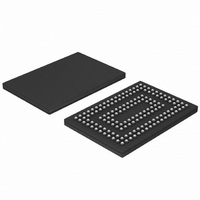

IC REG BUFFER 28BIT 160TFBGA

Manufacturer

NXP Semiconductors

Datasheet

1.SSTUB32865ETG518.pdf

(28 pages)

Specifications of SSTUB32865ET/G,518

Logic Type

1:2 Registered Buffer with Parity

Supply Voltage

1.7 V ~ 2 V

Number Of Bits

28

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

160-TFBGA

Logic Family

SSTU

Logical Function

Reg Bfr W/ParityTst

Number Of Elements

1

Number Of Inputs

28

Number Of Outputs

56

High Level Output Current

-8mA

Low Level Output Current

8mA

Propagation Delay Time

3ns

Operating Supply Voltage (typ)

1.8V

Operating Supply Voltage (max)

2V

Operating Supply Voltage (min)

1.7V

Clock-edge Trigger Type

Posit/Negat-Edge

Polarity

Non-Inverting

Technology

CMOS

Frequency (max)

450(Min)MHz

Mounting

Surface Mount

Pin Count

160

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

568-3542-2

935281691518

SSTUB32865ET/G-T

935281691518

SSTUB32865ET/G-T

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SSTUB32865ET/G,518

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

3. Applications

4. Ordering information

Table 1.

SSTUB32865_3

Product data sheet

Type number

SSTUB32865ET/G

SSTUB32865ET/S

Ordering information

4.1 Ordering options

Solder process

Pb-free (SnAgCu solder ball

compound)

Pb-free (SnAgCu solder ball

compound)

I

I

I

I

I

I

I

I

I

Table 2.

Type number

SSTUB32865ET/G

SSTUB32865ET/S

Chip-selects minimize power consumption by gating data outputs from changing state

Two additional chip select inputs allow optional flexible enabling and disabling

Supports Stub Series Terminated Logic SSTL_18 data inputs

Differential clock (CK and CK) inputs

Supports LVCMOS switching levels on the control and RESET inputs

Single 1.8 V supply operation (1.7 V to 2.0 V)

Available in 160-ball 9 mm

400 MT/s to 800 MT/s high-density (for example, 2 rank by 4) DDR2 registered DIMMs

DDR2 Registered DIMMs (RDIMM) desiring parity checking functionality

Ordering options

Rev. 03 — 27 March 2007

Temperature range

T

T

amb

amb

Package

Name

TFBGA160 plastic thin fine-pitch ball grid array package;

TFBGA160 plastic thin fine-pitch ball grid array package;

= 0 C to +70 C

= 0 C to +85 C

13 mm, 0.65 mm ball pitch TFBGA package

Description

160 balls; body 9

160 balls; body 9

1.8 V DDR2-800 registered buffer with parity

13

13

0.7 mm

0.7 mm

SSTUB32865

© NXP B.V. 2007. All rights reserved.

Version

SOT802-2

SOT802-2

2 of 28