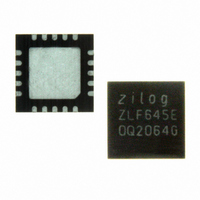

ZLF645E0Q2064G Zilog, ZLF645E0Q2064G Datasheet - Page 92

ZLF645E0Q2064G

Manufacturer Part Number

ZLF645E0Q2064G

Description

IC MCU 64K FLASH 1K RAM 20-QFN

Manufacturer

Zilog

Series

Crimzon™ ZLFr

Specifications of ZLF645E0Q2064G

Core Processor

Z8 LXMC

Core Size

8-Bit

Speed

8MHz

Connectivity

UART/USART

Peripherals

Brown-out Detect/Reset, HLVD, POR, WDT

Number Of I /o

16

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.9 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Oscillator Type

-

Other names

269-4723

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ZLF645E0Q2064G

Manufacturer:

Maxim

Quantity:

28

- Current page: 92 of 197

- Download datasheet (3Mb)

PS026407-0408

Note:

UART Interrupts

The UART is now configured for interrupt-driven data reception. When the UART

Receiver interrupt is detected, the associated ISR performs the following:

1. Checks the UART Status register to determine the source of the interrupt, whether it is

2. Reads the data from the UART Receive Data register, if the interrupt was caused by

3. Clears the UART receiver interrupt in the applicable Interrupt Request register.

4. Executes the IRET instruction to return from the ISR and await more data.

The UART features separate interrupts for the transmitter and the receiver. In addition,

when the UART primary functionality is disabled, the BRG can also function as a basic

timer with interrupt capability.

When the UART is set to run at higher baud rates, the UART receiver’s service routine

may not have enough time to read and manipulate all bits in the UART Status register

(especially bits generating error conditions) for a received byte before the next byte is

received. You can devise your own hand-shaking protocol to prevent the transmitter from

transmitting more data while current data is being serviced.

Transmitter Interrupts

The transmitter generates a single interrupt when the Transmit Status bit, UST[2], is set

to 1. This indicates that the transmitter is ready to accept new data for transmission. The

Transmit Status interrupt occurs after the internal transmit shift register has shifted the first

bit of data out. At this point, the Transmit Data register can be written with the next char-

acter to send. This provides 7 bit periods of latency to load the Transmit Data register

before the transmit shift register completes shifting the current character. Writing to the

UART Transmit Data register clears the UST[2] bit to 0. The interrupt is cleared by

writing a 0 to the Transmit Data register.

Receiver Interrupts

The receiver generates an interrupt when any of the following occurs:

•

•

an error, break, or received data.

data available.

A data byte is received and available in the UART Receive Data register—This

interrupt can be disabled independent of the other receiver interrupt sources. The

received data interrupt occurs once the receive character has been received and placed

in the Receive Data register. Software must respond to this received data available

condition before the next character is completely received to avoid an overrun error.

The interrupt is cleared by reading from the UART Receive Data register.

A break is received—A break is detected when a 0 is sent to the receiver for the full

byte plus the parity and stop bits. After a break is detected, it will interrupt

ZLF645 Series Flash MCUs

Product Specification

Operation

84

Related parts for ZLF645E0Q2064G

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Microcontrollers (MCU) Zlf645 (32K 20L Ssop F645 (32K 20L Ssop )

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products