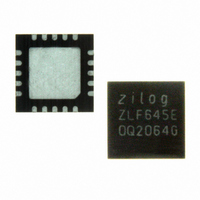

ZLF645E0Q2064G Zilog, ZLF645E0Q2064G Datasheet - Page 143

ZLF645E0Q2064G

Manufacturer Part Number

ZLF645E0Q2064G

Description

IC MCU 64K FLASH 1K RAM 20-QFN

Manufacturer

Zilog

Series

Crimzon™ ZLFr

Specifications of ZLF645E0Q2064G

Core Processor

Z8 LXMC

Core Size

8-Bit

Speed

8MHz

Connectivity

UART/USART

Peripherals

Brown-out Detect/Reset, HLVD, POR, WDT

Number Of I /o

16

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.9 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Oscillator Type

-

Other names

269-4723

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ZLF645E0Q2064G

Manufacturer:

Maxim

Quantity:

28

- Current page: 143 of 197

- Download datasheet (3Mb)

Table 68. Low-Voltage Detection Register (LVD)

PS026407-0408

Bit

Field

Reset

R/W

Address

Bit Position

[7:3]

[2]

Voltage Detection

Note:

R

7

1

To enter HALT mode, first flush the instruction pipeline to avoid suspending execution in

mid-instruction. Execute a NOP instruction (OpCode =

appropriate sleep instruction, as given below:

FF

7F

Power consumption during HALT mode can be reduced by first setting SMR[0]=1 to

enable the divide-by-16 clock prescaler.

The Low-Voltage Detection register (LVD, register 0Ch at the expanded register bank

0Dh) provides an option to monitor the V

when bit 0 of LVD register is set. After voltage detection is enabled, the V

monitored in real time. The HVD flag (bit 2 of the LVD register) is set only if V

higher than V

than the V

The IRQ bit 5 latches the low voltage condition until it is cleared by instructions or reset.

The IRQ5 interrupt is served if it is enabled in the IMR register. Otherwise, bit 5 of IRQ

register is latched as a flag only.

Do not modify register P01M while checking a low voltage condition. Switching noise

from Port 0 can trigger the LVD flag.

Value

—

0

1

R

6

1

LVD

Description

Reserved—Reads 11111b. Must be written to 1.

HVD clear.

High-voltage detected (V

Reserved

HVD.

. When voltage detection is enabled, the LVD flag also triggers IRQ5.

R

5

1

The LVD flag (bit 1 of the LVD register) is set only if V

NOP

HALT

R

4

1

Bank D: 0Ch; Linear: D0Ch

R

3

1

DD

; clear the pipeline

; enter HALT mode

>V

High-Battery

HVD)

DD

Detect

R

2

0

voltage. The voltage detection is enabled

Low-Battery

ZLF645 Series Flash MCUs

FFh

Detect

R

1

0

) immediately before the

Product Specification

Voltage Detection

Detect Enable

DD

Voltage

level is

DD

R/W

0

0

is lower

DD

is

135

Related parts for ZLF645E0Q2064G

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Microcontrollers (MCU) Zlf645 (32K 20L Ssop F645 (32K 20L Ssop )

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products