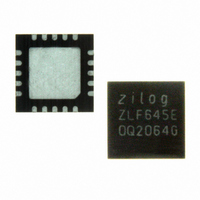

ZLF645E0Q2064G Zilog, ZLF645E0Q2064G Datasheet - Page 90

ZLF645E0Q2064G

Manufacturer Part Number

ZLF645E0Q2064G

Description

IC MCU 64K FLASH 1K RAM 20-QFN

Manufacturer

Zilog

Series

Crimzon™ ZLFr

Specifications of ZLF645E0Q2064G

Core Processor

Z8 LXMC

Core Size

8-Bit

Speed

8MHz

Connectivity

UART/USART

Peripherals

Brown-out Detect/Reset, HLVD, POR, WDT

Number Of I /o

16

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.9 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Oscillator Type

-

Other names

269-4723

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ZLF645E0Q2064G

Manufacturer:

Maxim

Quantity:

28

- Current page: 90 of 197

- Download datasheet (3Mb)

PS026407-0408

Caution:

Transmitting Data Using Interrupt-Driven Method

4. Check the Transmit Status register bit, UST[2], to determine if the Transmit Data

5. Write the data byte to the UART Transmit Data register,

6. To transmit additional bytes, return to

7. Before disabling the transmitter, read the transmit completion status bit, UST[1]. If

The UART transmitter interrupt indicates the availability of the Transmit Data register to

accept new data for transmission.

Follow the steps below to configure the UART for interrupt-driven data transmission:

1. Write to the BCNST register to set the appropriate baud rate.

2. Write 0 to bit 6 of the P01M register.

3. Execute DI instruction to disable interrupts.

4. Write to the Interrupt Control registers to enable the UART Transmitter interrupt and

5. Write to the UART Control register to:

6. Execute an EI instruction to enable interrupts as the transmit buffer is empty, an

7. Write the data byte to the UART Transmit Data register. The transmitter automatically

8. Execute the IRET instruction to return from the interrupt service routine (ISR) and

Data written while the transmit enable bit is clear (UCTL[7]=0) will not be transmitted.

Data written while the transmit data status bit is clear (UST[2]=0) overwrites the

previous value written, so the previous written value will not be transmitted. Disabling

the UART transmitter while the transmit completion status bit is clear (UST[1]=0) can

corrupt the byte being transmitted.

register is empty (indicated by 1). If empty, continue to

register is full (indicated by 0), continue to monitor the UST[2] bit until the Transmit

Data register is available to receive new data.

automatically transfers the data to the internal transmit shift register and transmits the

data.

UST[1]=0, continue to monitor the bit until it changes to 1, which indicates that all

data in the Transmit Data and internal shift registers has been transmitted.

set the appropriate priority.

(a) Set the transmit enable bit (UCTL bit 7) to enable the UART for data transmission.

(b) Enable parity, if appropriate, and select either even- or odd-parity.

interrupt is immediately executed.

transfers the data to the Internal Transmit Shift register and transmits the data.

wait for the Transmit Data register to again become empty.

Step

4.

ZLF645 Series Flash MCUs

0F1h

Step

Product Specification

. The transmitter

6. If the Transmit Data

Operation

82

Related parts for ZLF645E0Q2064G

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Microcontrollers (MCU) Zlf645 (32K 20L Ssop F645 (32K 20L Ssop )

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products

Part Number:

Description:

Microcontrollers (MCU) Crimzon Flash Infrared MCU

Manufacturer:

Maxim Integrated Products