Chameleon-PIC Nurve Networks, Chameleon-PIC Datasheet - Page 182

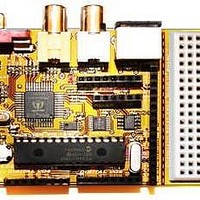

Chameleon-PIC

Manufacturer Part Number

Chameleon-PIC

Description

MCU, MPU & DSP Development Tools PIC24 & PROPELLER DEV SYSTEM (SBC)

Manufacturer

Nurve Networks

Datasheet

1.CHAMELEON-PIC.pdf

(263 pages)

Specifications of Chameleon-PIC

Processor To Be Evaluated

PIC24

Data Bus Width

16 bit

Interface Type

USB, VGA, PS/2, I2C, ISP, SPI

Operating Supply Voltage

3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

22.2 Header File Contents Overview

Since the GFX driver is a special case, I want to re-enforce that its worth reviewing the Propeller side driver as well, so

you can see what’s really going on. We are only going to cover the C/PIC side of things here, but all these registers,

functions, API, etc. are all handled at some point on the Propeller running the enhanced graphics driver for NTSC tile

graphics. With that in mind, let’s crack open the C/C++ header file named: CHAM_PIC_GFX_DRV_V010.h and see

what’s inside. If you look inside the file, you will see nothing other than a conditional compilation section and the

prototypes for the function API, so where are all the register interface defines? Well, remember we have to keep all the

SPI commands in a single place, so the register interface are actually message IDs for the SPI messaging system! Thus,

if you open up CHAM_PIC_I2C_SPI_DRV_V010.h and scroll down then you will get to the section with the register

interface messages for the GFX driver itself, they are:

// advanced GFX commands for GFX tile engine

#define

#define

#define

#define

// normal commands

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

// gpu configuration registers

#define

#define

// sub-function constants that are executed when the GPU_GFX_SUBFUNC_STATUS_W command is issued

#define GPU_GFX_SUBFUNC_COPYMEM16 0 // Copies numbytes from src -> dest in wordsize chunks

#define GPU_GFX_SUBFUNC_FILLMEM16 1 // Fills memory with data16, 2 bytes at a time

#define GPU_GFX_SUBFUNC_COPYMEM8

#define GPU_GFX_SUBFUNC_FILLMEM8

GPU_GFX_BASE_ID

GPU_GFX_NUM_COMMANDS

GPU_GFX_SUBFUNC_STATUS_R

GPU_GFX_SUBFUNC_STATUS_W

GPU_GFX_TILE_MAP_R

GPU_GFX_TILE_MAP_W

GPU_GFX_DISPLAY_PTR_R

GPU_GFX_DISPLAY_PTR_W

GPU_GFX_TERM_PTR_R

GPU_GFX_TERM_PTR_W

GPU_GFX_BITMAP_R

GPU_GFX_BITMAP_W

GPU_GFX_PALETTE_R

GPU_GFX_PALETTE_W

GPU_GFX_TOP_OVERSCAN_COL_R (12+GPU_GFX_BASE_ID) // Reads top overscan color drawn on the screen.

GPU_GFX_TOP_OVERSCAN_COL_W (13+GPU_GFX_BASE_ID) // Writes top overscan color drawn on the screen.

GPU_GFX_BOT_OVERSCAN_COL_R (14+GPU_GFX_BASE_ID) // Reads top overscan color drawn on the screen.

GPU_GFX_BOT_OVERSCAN_COL_W (15+GPU_GFX_BASE_ID) // Writes top overscan color drawn on the screen.

GPU_GFX_HSCROLL_FINE_R

GPU_GFX_HSCROLL_FINE_W

GPU_GFX_VSCROLL_FINE_R

GPU_GFX_VSCROLL_FINE_W

GPU_GFX_SCREEN_WIDTH_R

GPU_GFX_SCREEN_WIDTH_W

GPU_GFX_SRC_ADDR_R

GPU_GFX_SRC_ADDR_W

GPU_GFX_DEST_ADDR_R

GPU_GFX_DEST_ADDR_W

GPU_GFX_NUM_BYTES_R

GPU_GFX_NUM_BYTES_W

GPU_GFX_DATA_R

GPU_GFX_DATA_W

GPU_GFX_RAM_PORT8_R

GPU_GFX_RAM_PORT8_W

GPU_GFX_RAM_PORT16_R

GPU_GFX_RAM_PORT16_W

GPU_GFX_RASTER_LINE_R

GPU_GFX_SET_AUTO_INC_R

GPU_GFX_SET_AUTO_INC_W

192

37

(16+GPU_GFX_BASE_ID)

(17+GPU_GFX_BASE_ID)

(18+GPU_GFX_BASE_ID) // Reads current fine vertical scroll register (0..7)

(19+GPU_GFX_BASE_ID) // Writes current fine vertical scroll register (0..7)

(20+GPU_GFX_BASE_ID) // Reads screen width value, 0=16 tiles, 1=32 tiles, 2=64 tiles, etc.

(21+GPU_GFX_BASE_ID) // Writes screen width value, 0=16 tiles, 1=32 tiles, 2=64 tiles, etc.

(22+GPU_GFX_BASE_ID) // Reads 16-bit source address for GPU operations.

(23+GPU_GFX_BASE_ID) // Writes 16-bit source address for GPU operations.

(24+GPU_GFX_BASE_ID) // Reads 16-bit destination address for GPU operations.

(25+GPU_GFX_BASE_ID) // Writes 16-bit destination address for GPU operations.

(26+GPU_GFX_BASE_ID) // Reads 16-bit number representing the number of bytes for a GPU operation Sub-Function.

(27+GPU_GFX_BASE_ID) // Writes 16-bit number representing the number of bytes for a GPU operation Sub-Function.

(28+GPU_GFX_BASE_ID) // Reads 16-bit data word uses for GPU operations or memory access operations.

(29+GPU_GFX_BASE_ID) // Writes 16-bit data word uses for GPU operations or memory access operations.

(30+GPU_GFX_BASE_ID) // Reads 8-bit data pointed to by the currently addressed memory location in the GPU pointed to

(31+GPU_GFX_BASE_ID) // Writes 8-bit data pointed to by the currently addressed memory location in the GPU pointed

(32+GPU_GFX_BASE_ID) // Reads 16-bit data pointed to by the currently addressed memory location in the GPU pointed

(33+GPU_GFX_BASE_ID) // Writes 16-bit data pointed to by the currently addressed memory location in the GPU pointed

(34+GPU_GFX_BASE_ID) // Reads the current raster line being drawn from 0..191, or whatever the GPU's line resolution

(35+GPU_GFX_BASE_ID) // Reads current memory auto increment setting for read/write operations lower 4-bits (0..15),

(36+GPU_GFX_BASE_ID) // Writes the current memory auto increment setting for read/write operations lower 4-bits

(0+GPU_GFX_BASE_ID) // Reads the status of the GPU, Writes the GPU Sub-Function register and issues a high level

(1+GPU_GFX_BASE_ID) // Writes status of the GPU, Writes the GPU Sub-Function register and issues a high level

(2+GPU_GFX_BASE_ID) // Reads 16-bit tile map ptr which points to the current tile map displayed.

(3+GPU_GFX_BASE_ID) // Writes 16-bit tile map ptr which points to the current tile map displayed.

(4+GPU_GFX_BASE_ID) // Reads 16-bit tile map ptr which points to the current display ptr into the tile map, low

(5+GPU_GFX_BASE_ID) // Writes 16-bit tile map ptr which points to the current display ptr into the tile map, low

(6+GPU_GFX_BASE_ID) // Reads 16-bit tile map ptr which points to the current terminal ptr into the tile map,

(7+GPU_GFX_BASE_ID) // Writes 16-bit tile map ptr which points to the current terminal ptr into the tile map,

(8+GPU_GFX_BASE_ID) // Reads 16-bit tile bitmaps ptr which points to the bitmaps indexed by the tilemap.

(9+GPU_GFX_BASE_ID) // Reads 16-bit tile bitmaps ptr which points to the bitmaps indexed by the tilemap.

(10+GPU_GFX_BASE_ID) // Reads 16-bit palette array ptr which points to the palettes in use for the tilemap.

(11+GPU_GFX_BASE_ID) // Writes 16-bit palette array ptr which points to the palettes in use for the tilemap.

2 // Copies numbytes from src -> dest in byte size chunks

3 // Fills memory with low byte of data16, 1 bytes at a time

// by the src_addr_low|hi.

// After the operation, the src_addr_ptr is incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_add_rptr are incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_addr_ptr is incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_add_rptr are incremented as per the GPU configuration.

// is set to.

// default 0

// (0..15), default 0

// starting id for GFX commands to keep them away from normal command set

// number of GFX commands

// command like copy, fill, etc.

// command like copy, fill, etc.

// level print functions use this pointer.

// level print functions use this pointer.

// terminal level print functions use this pointer.

// terminal level print functions use this pointer.

// Reads current fine horizontal scroll register (0..7) NOTE: (NOT implemented yet)

// Writes current fine horizontal scroll register (0..7) NOTE: (NOT implemented yet)

© 2009 NURVE NETWORKS LLC “Exploring the Chameleon PIC 16-Bit”

182