Chameleon-PIC Nurve Networks, Chameleon-PIC Datasheet - Page 163

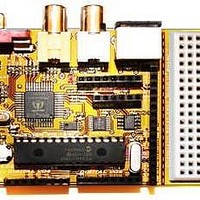

Chameleon-PIC

Manufacturer Part Number

Chameleon-PIC

Description

MCU, MPU & DSP Development Tools PIC24 & PROPELLER DEV SYSTEM (SBC)

Manufacturer

Nurve Networks

Datasheet

1.CHAMELEON-PIC.pdf

(263 pages)

Specifications of Chameleon-PIC

Processor To Be Evaluated

PIC24

Data Bus Width

16 bit

Interface Type

USB, VGA, PS/2, I2C, ISP, SPI

Operating Supply Voltage

3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 163 of 263

- Download datasheet (12Mb)

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

#define

// gpu configuration registers

#define

#define

And that’s about it for #defines, let’s move on to the API roadmap.

19.4 API Listing Reference

The API listing for the “SPI and I

hardware functionality. The SPI API is more developed since the I2C tends to have a lot “state” in it, functions have to

return with errors and other information, hence, you will probably want to write your own functions in the future.

Nonetheless, I have included an I2C initialization and WaitTillIdle command that does some of the work for you. Its best

however to read up on the I2C registers provided by the PIC peripheral and use the registers explicitly since they are so

application specific. Table 19.2 below lists the “SPI and I

Function Name

I2C related functions

void I2C_Init(unsigned long ClockHz);

void I2C_WaitTillIdle();

GPU_GFX_DISPLAY_PTR_R

GPU_GFX_DISPLAY_PTR_W

GPU_GFX_TERM_PTR_R

GPU_GFX_TERM_PTR_W

GPU_GFX_BITMAP_R

GPU_GFX_BITMAP_W

GPU_GFX_PALETTE_R

GPU_GFX_PALETTE_W

GPU_GFX_TOP_OVERSCAN_COL_R (12+GPU_GFX_BASE_ID) // Reads top overscan color drawn on the screen.

GPU_GFX_TOP_OVERSCAN_COL_W (13+GPU_GFX_BASE_ID) // Writes top overscan color drawn on the screen.

GPU_GFX_BOT_OVERSCAN_COL_R (14+GPU_GFX_BASE_ID) // Reads top overscan color drawn on the screen.

GPU_GFX_BOT_OVERSCAN_COL_W (15+GPU_GFX_BASE_ID) // Writes top overscan color drawn on the screen.

GPU_GFX_HSCROLL_FINE_R

GPU_GFX_HSCROLL_FINE_W

GPU_GFX_VSCROLL_FINE_R

GPU_GFX_VSCROLL_FINE_W

GPU_GFX_SCREEN_WIDTH_R

GPU_GFX_SCREEN_WIDTH_W

GPU_GFX_SRC_ADDR_R

GPU_GFX_SRC_ADDR_W

GPU_GFX_DEST_ADDR_R

GPU_GFX_DEST_ADDR_W

GPU_GFX_NUM_BYTES_R

GPU_GFX_NUM_BYTES_W

GPU_GFX_DATA_R

GPU_GFX_DATA_W

GPU_GFX_RAM_PORT8_R

GPU_GFX_RAM_PORT8_W

GPU_GFX_RAM_PORT16_R

GPU_GFX_RAM_PORT16_W

GPU_GFX_RASTER_LINE_R

GPU_GFX_SET_AUTO_INC_R

GPU_GFX_SET_AUTO_INC_W

(16+GPU_GFX_BASE_ID)

(17+GPU_GFX_BASE_ID)

(18+GPU_GFX_BASE_ID) // Reads current fine vertical scroll register (0..7)

(19+GPU_GFX_BASE_ID) // Writes current fine vertical scroll register (0..7)

(20+GPU_GFX_BASE_ID) // Reads screen width value, 0=16 tiles, 1=32 tiles, 2=64 tiles, etc.

(21+GPU_GFX_BASE_ID) // Writes screen width value, 0=16 tiles, 1=32 tiles, 2=64 tiles, etc.

(22+GPU_GFX_BASE_ID) // Reads 16-bit source address for GPU operations.

(23+GPU_GFX_BASE_ID) // Writes 16-bit source address for GPU operations.

(24+GPU_GFX_BASE_ID) // Reads 16-bit destination address for GPU operations.

(25+GPU_GFX_BASE_ID) // Writes 16-bit destination address for GPU operations.

(26+GPU_GFX_BASE_ID) // Reads 16-bit number representing the number of bytes for a GPU operation Sub-Function.

(27+GPU_GFX_BASE_ID) // Writes 16-bit number representing the number of bytes for a GPU operation Sub-Function.

(28+GPU_GFX_BASE_ID) // Reads 16-bit data word uses for GPU operations or memory access operations.

(29+GPU_GFX_BASE_ID) // Writes 16-bit data word uses for GPU operations or memory access operations.

(30+GPU_GFX_BASE_ID) // Reads 8-bit data pointed to by the currently addressed memory location in the GPU pointed to

(31+GPU_GFX_BASE_ID) // Writes 8-bit data pointed to by the currently addressed memory location in the GPU pointed

(32+GPU_GFX_BASE_ID) // Reads 16-bit data pointed to by the currently addressed memory location in the GPU pointed

(33+GPU_GFX_BASE_ID) // Writes 16-bit data pointed to by the currently addressed memory location in the GPU pointed

(34+GPU_GFX_BASE_ID) // Reads the current raster line being drawn from 0..191, or whatever the GPU's line resolution

(35+GPU_GFX_BASE_ID) // Reads current memory auto increment setting for read/write operations lower 4-bits (0..15),

(36+GPU_GFX_BASE_ID) // Writes the current memory auto increment setting for read/write operations lower 4-bits

(4+GPU_GFX_BASE_ID) // Reads 16-bit tile map ptr which points to the current display ptr into the tile map, low

(5+GPU_GFX_BASE_ID) // Writes 16-bit tile map ptr which points to the current display ptr into the tile map, low

(6+GPU_GFX_BASE_ID) // Reads 16-bit tile map ptr which points to the current terminal ptr into the tile map,

(7+GPU_GFX_BASE_ID) // Writes 16-bit tile map ptr which points to the current terminal ptr into the tile map,

(8+GPU_GFX_BASE_ID) // Reads 16-bit tile bitmaps ptr which points to the bitmaps indexed by the tilemap.

(9+GPU_GFX_BASE_ID) // Reads 16-bit tile bitmaps ptr which points to the bitmaps indexed by the tilemap.

(10+GPU_GFX_BASE_ID) // Reads 16-bit palette array ptr which points to the palettes in use for the tilemap.

(11+GPU_GFX_BASE_ID) // Writes 16-bit palette array ptr which points to the palettes in use for the tilemap.

Table 19.2 – “SPI and I

2

C” module CHAM_PIC_I2C_SPI_V010.c supports a thin “wrapper” layer over the

// by the src_addr_low|hi.

// After the operation, the src_addr_ptr is incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_add_rptr are incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_addr_ptr is incremented as per the GPU configuration.

// to by the src_addr_low|hi.

// After the operation, the src_add_rptr are incremented as per the GPU configuration.

// is set to.

// default 0

// (0..15), default 0

// level print functions use this pointer.

// level print functions use this pointer.

// terminal level print functions use this pointer.

// terminal level print functions use this pointer.

// Reads current fine horizontal scroll register (0..7) NOTE: ( NOT implemented yet)

// Writes current fine horizontal scroll register (0..7) NOTE: ( NOT implemented yet)

2

C” module API functions listing.

2

C” API functions categorized by functionality.

© 2009 NURVE NETWORKS LLC “Exploring the Chameleon PIC 16-Bit”

Description

Initializes the I2C hardware.

Pauses execution until an Idle state is found.

163

Related parts for Chameleon-PIC

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools PIC24 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 & PROPELLER DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Datasheet: