HD64F38024DV Renesas Electronics America, HD64F38024DV Datasheet - Page 949

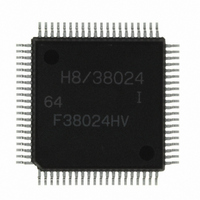

HD64F38024DV

Manufacturer Part Number

HD64F38024DV

Description

IC H8/SLP MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300L SLPr

Datasheets

1.US38024-BAG1.pdf

(684 pages)

2.DF36012GFYV.pdf

(1021 pages)

3.DF38102HV.pdf

(145 pages)

Specifications of HD64F38024DV

Core Processor

H8/300L

Core Size

8-Bit

Speed

10MHz

Connectivity

SCI

Peripherals

LCD, PWM, WDT

Number Of I /o

51

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

HD64F38024DV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 949 of 1021

- Download datasheet (5Mb)

2. cpuexpand (from Ver. 6.01)

3. code=asmcode (from Ver. 6.01)

4. Changed Section for Explicitly Initialized Variables (from Ver. 6.01)

5. Object Format (from Ver. 4.0)

6. Added an Option to Modify the Function Interface (from Ver. 4.0)

If cpuexpand is specified, the result of some operations may differ from those produced by

earlier versions of the compiler (Ver.4.x or earlier). To obtain uniform results, specify

legacy=v4 for compilation when the CPU type setting is 2600A, 2600N, 2000A, or 2000N, or

specify cpuexpand for all files and recompile them when the CPU type setting is any of the

H8SX variants. For the expressions that produce variable results, refer to the description of

cpuexpand=v6 in section 2.2.2, Object Options.

From this version (Ver.6.01), the compiler outputs a .STACK directive within the assembly-

source program if code=asmcode is specified. Thus the assembler for use must be Ver.6.01,

which supports .STACK.

In Ver.6.00.00, explicitly initialized variables for which H8/300, H8/300H, H8S/2000, or

H8S/2600 had been specified as the CPU type were output to section D.

In Ver.6.00.01, if the CPU type is H8S/2000 or H8S/2600, explicitly initialized variables are

output to section C. If the CPU type is H8/300 or H8/300H, explicitly initialized variables are

still output to section D. With the H8SX setting, however, explicitly initialized variables are

always output to section C, regardless of the compiler version.

The object file format has been changed from SYSROF to the standard format ELF. The

debugging information format has also been changed to the standard format DWARF2.

Before an object file (SYSROF) output by Ver. 3.x or earlier of the compiler or assembler is to

input to the latest optimizing linkage editor, use a file converter to convert it to the ELF format.

However, relocatable files output by the linkage editor (extension: rel) and library files that

include one or more relocatable files cannot be converted.

When a debugger which supports the SYSROF or ELF/DWARF1format load modules is used,

use the file converter to convert the load module from the ELF/DWARF2 format to the

SYSROF or ELF/DWARF1 format. However, the debugging information will not be

converted and only the object part will be valid if #pragma option (new feature of Ver. 4.0

compiler) has created a file in which a function with optimization and that without

optimization coexist.

Options structreg and longreg have been added to modify the function interface rules.

Recompile all files after you have specified either option. Modify the interfaces of assembly

routines, too.

935

Related parts for HD64F38024DV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet: