EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 298

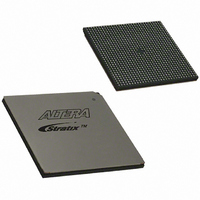

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 298 of 864

- Download datasheet (11Mb)

Contents

Chapter 5. High-Speed Differential I/O Interfaces in Stratix Devices

vi

Drive Strength ...................................................................................................................................... 4–26

Hot Socketing ....................................................................................................................................... 4–27

I/O Termination .................................................................................................................................. 4–28

I/O Pad Placement Guidelines .......................................................................................................... 4–30

Power Source of Various I/O Standards ......................................................................................... 4–38

Quartus II Software Support .............................................................................................................. 4–38

Conclusion ............................................................................................................................................ 4–42

More Information ................................................................................................................................ 4–42

References ............................................................................................................................................. 4–42

Introduction ............................................................................................................................................ 5–1

Stratix I/O Banks ................................................................................................................................... 5–1

Principles of SERDES Operation ......................................................................................................... 5–6

Using SERDES to Implement DDR ................................................................................................... 5–13

Using SERDES to Implement SDR .................................................................................................... 5–14

Differential I/O Interface & Fast PLLs ............................................................................................. 5–16

Mixing Voltage Referenced & Non-Voltage Referenced Standards ....................................... 4–25

Standard Current Drive Strength ................................................................................................. 4–26

Programmable Current Drive Strength ...................................................................................... 4–27

DC Hot Socketing Specification ................................................................................................... 4–28

AC Hot Socketing Specification ................................................................................................... 4–28

Voltage-Referenced I/O Standards ............................................................................................. 4–28

Differential I/O Standards ............................................................................................................ 4–29

Differential Termination (RD) ...................................................................................................... 4–29

Transceiver Termination ............................................................................................................... 4–30

Differential Pad Placement Guidelines ....................................................................................... 4–30

VREF Pad Placement Guidelines ................................................................................................. 4–31

Output Enable Group Logic Option in Quartus II .................................................................... 4–34

Toggle Rate Logic Option in Quartus II ...................................................................................... 4–35

DC Guidelines ................................................................................................................................. 4–35

Compiler Settings ........................................................................................................................... 4–38

Device & Pin Options .................................................................................................................... 4–39

Assign Pins ...................................................................................................................................... 4–39

Programmable Drive Strength Settings ...................................................................................... 4–40

I/O Banks in the Floorplan View ................................................................................................. 4–40

Auto Placement & Verification of Selectable I/O Standards ................................................... 4–41

Stratix Differential I/O Standards ................................................................................................. 5–2

Stratix Differential I/O Pin Location ............................................................................................. 5–5

Stratix Differential I/O Receiver Operation ................................................................................. 5–7

Stratix Differential I/O Transmitter Operation ........................................................................... 5–9

Transmitter Clock Output ............................................................................................................. 5–10

Divided-Down Transmitter Clock Output ................................................................................. 5–10

Center-Aligned Transmitter Clock Output ................................................................................ 5–11

SDR Transmitter Clock Output .................................................................................................... 5–12

Clock Input & Fast PLL Output Relationship ............................................................................ 5–18

Fast PLL Specifications .................................................................................................................. 5–20

Stratix Device Handbook, Volume 2

Altera Corporation

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: